# **Manual Update Sheet**

**DATE: January 31, 2003**

Document Being Updated: TMS320C6000 Peripherals Reference Guide

Literature Number Being Updated: SPRU190D

This Manual Update Sheet (SPRZ122C) describes changes for the TMS320C6000 Peripherals Reference Guide (SPRU190D).

Updates within paragraphs, figures, and tables appear in a **bold typeface**.

**Change or Add:** Page:

1-9 Add a C6416 column and a VCP/TCP coprocessors row, change the footnote in Table 1–2:

Table 1–2. TMS320C6000 Peripherals

| Peripheral                                                  | C6201 | C6202(B)<br>C6203(B) | C6204 | C6205 | C621x | C6414 | C6415          | C6416          | C6701 | C671x |

|-------------------------------------------------------------|-------|----------------------|-------|-------|-------|-------|----------------|----------------|-------|-------|

| Direct memory<br>access (DMA)<br>controller                 | Υ     | Υ                    | Y     | Υ     | N     | N     | N              | N              | Υ     | N     |

| Enhanced<br>direct memory<br>access<br>(EDMA)<br>controller | N     | N                    | N     | N     | Y     | Y     | Y              | Y              | N     | Y     |

| Host-port interface (HPI)                                   | Υ     | N                    | N     | N     | Υ     | Υ     | Υ <sup>†</sup> | Y <sup>†</sup> | Υ     | Υ     |

| Expansion bus (XBUS)                                        | N     | Υ                    | Υ     | N     | N     | N     | N              | N              | N     | N     |

| PCI                                                         | Ν     | N                    | N     | Υ     | N     | N     | Y <sup>†</sup> | Υ <sup>†</sup> | N     | N     |

| External<br>memory<br>interface<br>(EMIF)                   | 1     | 1                    | 1     | 1     | 1     | 2     | 2              | 2              | 1     | 1     |

| Boot configuration                                          | Υ     | Υ                    | Υ     | Υ     | Υ     | Υ     | Υ              | Υ              | Υ     | Υ     |

| Multichannel<br>buffered serial<br>ports<br>(McBSPs)        | 2     | 3                    | 2     | 2     | 2     | 3     | 3†             | 3†             | 2     | 2     |

| UTOPIA                                                      | Ν     | N                    | N     | N     | N     | N     | Y <sup>†</sup> | Y <sup>†</sup> | N     | N     |

| Interrupt<br>selector                                       | Υ     | Υ                    | Y     | Υ     | Υ     | Υ     | Υ              | Υ              | Υ     | Υ     |

| 32-bit timers                                               | 2     | 2                    | 2     | 2     | 2     | 3     | 3              | 3              | 2     | 2     |

| Power-down logic                                            | Υ     | Υ                    | Υ     | Υ     | Υ     | Υ     | Υ              | Υ              | Υ     | Υ     |

| Peripheral           | C6201 | C6202(B)<br>C6203(B) | C6204 | C6205 | C621x | C6414 | C6415 | C6416 | C6701 | C671x |

|----------------------|-------|----------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| GPIO<br>peripheral   | N     | N                    | N     | N     | N     | Y     | γ†    | γ†    | N     | N     |

| VCP/TCP coprocessors | N     | N                    | N     | N     | N     | N     | N     | Υ     | N     | N     |

<sup>&</sup>lt;sup>†</sup> The C6415/C6416 peripheral set is selected at device reset. For details, see *Chapter 11*, *Boot Modes and Configuration*, and the specific device datasheet.

#### 2–3 Change the last paragraph in section 2.2:

Table 2–1 and Table 2–2 compare the internal memory and cache configurations available on the current TMS320C6x0x devices. Figure 2–2 shows a block diagram of the connections between the C6201/C6204/C6205/C6701 CPU, PMEMC, and memory blocks. Figure 2–3 shows a block diagram of the connections between the CPU, PMEMC, and memory blocks in the C6202/C6202B/C6203(B). For C6202(B)/C6203(B), there are two program memory controllers, PMEM1 and PMEM0. The PMEM1 controller handles all accesses to program memory block 1 (SRAM and cache), as well as all cache operations and external accesses. The PMEM0 controller always accesses program memory block 0 (SRAM only). The addresses shown in Figure 2–2 and Figure 2–3 are for operation in memory map mode 1.

#### 2–12 Add to the end of the paragraph in section 2.2.6:

While the CPU is executing from external memory, IPRAM block 1 can not be accessed using the DMA. The PMEM1 memory controller is used by the CPU to fetch instructions from the EMIF, therefore while performing a fetch from external memory, DMA access to PMEM1 is limited.

#### 2–12 Add a new section 2.2.7:

#### 2.2.7 Illegal Access to Program Memory

An access to a section of memory that does not return a ready indication is not allowed. Possible requestors are: CPU program fetches, CPU loads and stores, programmed DMA channels or HPI/PCI/XBUS host mastering of the DMA through the auxiliary DMA. This type of access can create a stall indefinitely. When a requestor has created a program memory stall, other requestors are unable to access this program memory space. For C6202/C6203, if an access generates a program memory block 0 stall, other requestors may still access program memory block 1 and vice versa.

2–24 Add a new section 2.4.8. The subsequent sections are renumbered accordingly:

#### 2.4.8 Illegal Access to Data Memory

An access to a section of memory that does not return a ready indication is not allowed. Possible requestors are: CPU program fetches, CPU loads and stores, programmed DMA channels or HPI/PCI/XBUS host mastering of the DMA through the auxiliary DMA. This type of access can create a stall indefinitely. When a requestor has created a data memory stall, other requestors are unable to access this data memory space.

- 3–all Chapter 3: TMS320C621x/C671x/C64x Two-Level Internal Memory. This chapter has been revised and divided into two new documents: TMS320C621x/C671x Two-Level Internal Memory (SPRU609) and TMS320C64x Two-Level Internal Memory (SPRU610). Updates to Chapter 3 that are not yet applied in those two new documents are documented in this manual update sheet.

- 3–11 Change the first paragraph in section 3.3.3:

The L2 operates in four operation modes, depending on the state of the CCFG register. **CPU** may only perform read/write access to L2 addresses which are mapped as SRAM. Undefined operation may occur if CPU reads/writes from/to L2 addresses acting as cache. Figure 3–6 shows the division of the L2 SRAM into mapped memory space and cache for each TMS320C621x/C671x L2 Mode. It also shows how the memory configuration for the L2 affects the proportion of cache and SRAM.

3–18 Change the title in section 3.4.4:

#### 3.4.4 L1D Memory Banking Structure

- 3–33 Delete the last sentence of section 3.6.1: Since the L1D and L2 could be incoherent due to write hits in the L1D, the user should perform an L1D invalidation to force any dirty L1D data into the L2.

- 3–35 Change the paragraph in section 3.6.3:

Figure 3–26 shows four L1D misses when the L2 segment is configured as cache. The pipeline signals are explained in Figure 3–27. In this scenario, the CPU requests data in clock cycle 0 for read1 and read 2. In clock cycle 1 the data is looked for in L1D. The data is not present in L1D so in cycle 2 a miss is recorded for both read1 and read2. Also in cycle 1 the CPU requests the data for read3 and read4. In cycle 3, there is an L2 request for the data for read1 and a miss is recorded for both read3 and read4. In cycles 4, 7, and 9 there are L2 requests for the data for read2, read3, and read4, respectively. In cycles 9 and 10, the data for read1 is found in L2 and placed in L1. In cycles 11 and 12, the data for read2 is found in L2 and placed in L1. In cycle 13, the data from read1 and read2 is placed in the register file. Also in cycle 13 and in cycle 14 the data from read3 is found in L2 and placed in L1. In cycles 15 and 16 the data from read4 is found in L2 and placed in L1. In cycle 17, the data from read3 and read4 is placed in the register file. For these four misses, the CPU was stalled for a total of 14 clock cycles. This averages 4.67 cycles instead of 8 cycles for a single miss.

3–39 Change the paragraph below Table 3–10:

The reset value of the L2MODE field is 000b, thus the L2 RAM is configured as mapped SRAM at reset to support data boot-loading. Any L2 RAM that is configured as cache is no longer in the memory map. For example, in L2 mode 010b the address range from **000F 0000h to 000F FFFFh** is no longer available in the TMS320C64x memory map. The associativity of the L2 cache RAM is a function of the L2 Mode on the C671x and C621x but stays at four-way for the C64x architecture. On C621x/C671x each \(^{1}\)4 of SRAM added in the cache increases the associativity by one line per set. To ensure coherency and data integrity on an L2 mode switch, the user must perform a series of operations.

3–40 Change the second paragraph in section 3.7.2:

The L2 SRAM is made up of four 64-bit-wide memory banks on the C621x/C671x, and eight 64-bit-wide memory banks on the C64x. Since the L1P data bus is 256-bits wide, any L1P request that occurs at the same time as an L1D or EDMA request will cause a bank collision and, therefore, a stall.

3–41 Add section 3.7.2.1, Figure 3–29, and Table 3–12. The subsequent figures and tables are renumbered accordingly:

#### 3.7.2.1 L2 Write Hits vs. EDMA Priority (C64x only)

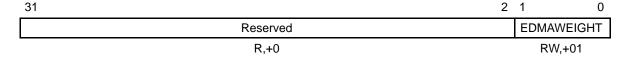

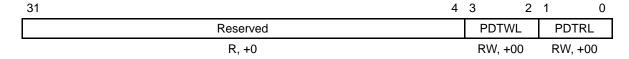

C64x devices (revision 1.1 and later) incorporate a register to give EDMA accesses a temporary boost in priority so that they can meet real-time needs. This priority boost only applies when competing with write data from the CPU that misses in L1D, but hits in L2 cache or L2 SRAM. The EDMA weight register (EDMAWEIGHT) lets you control how often this priority boost is given. When EDMA priority is raised, it is allowed to complete one access before priority is returned to the CPU data. The EDMAWEIGHT is shown in Figure 3–29 and summarized in Table 3–12.

Figure 3–29. TMS320C64x EDMA Weight Register (EDMAWEIGHT)

Table 3–12. TMS320C64x EDMA Weight Register (EDMAWEIGHT) Field Description

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EDMAWEIGHT | Allows EDMA priority raised over L1D–L2 writes once every N CPU cycles.  EDMAWEIGHT=00: L1D 100%, EDMA 0%, EDMA never gets priority over L1D.  EDMAWEIGHT=01: L1D 94%, EDMA 6%, EDMA gets priority every 16 cycles (default).  EDMAWEIGHT=10: L1D 80%, EDMA 20%, EDMA gets priority every 4 cycles.  EDMAWEIGHT=11: L1D 50%, EDMA 50%, EDMA gets priority every other cycle. |

3–41 Add section 3.7.3. The subsequent sections are renumbered accordingly.

#### 3.7.3 Data Endianness

The data endianness of C621x/C671x/C64x is the same as C620x/C670x. See section 2.4.8, *Data Endianness*, for details.

#### 3–41 Change the paragraph in section 3.7.3:

When an L2 location is enabled as a cache, the operation is similar to the L1D cache. On a read request to the L2 the data is sent to the requestor if a hit occurs. If the data is not in the L2 the requestor is stalled and the Least Recently Used(LRU) line is allocated for the new data. If the allocated line contains valid data the L1D is snooped. The L1D must be snooped even if an L1P miss supplied the L2 miss address because the evicted L2 line could be cached in the L1D. If the L1D returns data both the matching L1D line and evicted L2 line are invalidated, otherwise only the evicted L2 line is invalidated. Both the L2 and L1D caches must be invalidated on an L1D match to maintain coherency between the caches. If the L1D returns dirty data or if the evicted L2 line contains dirty data that data is evicted to the external memory and the required data is requested from the Enhanced DMA. The L2 is a load through cache, thus when servicing L1/L2 misses, data is stored in both L1 and L2 simultaneously. To minimize the CPU stall time, the L2 will fetch misses so that the data needed by L1 is returned first, followed by the rest of the L2 line. When the requested L1 data is available from the EDMA, the L2 will immediately forward it to L1 and unstall the CPU, and then wait for the remainder of the L2 line from the EDMA.

#### 4–4 Change the paragraph before Figure 4–1:

Figure 4–1 shows the TMS320C6000 block diagram with the DMA-related components shaded. **Table 4–1** summarizes the differences between the DMAs in different C6000 devices.

# 4–11 Change the bit name of bits 18–16 in Figure 4–3:

Figure 4–3. DMA Channel Secondary Control Register (SECCTL)

| 31           |               |              |               |             |               |             | 22            | :           | 21            | 20         |              | 19          | 18            |          | 16         |

|--------------|---------------|--------------|---------------|-------------|---------------|-------------|---------------|-------------|---------------|------------|--------------|-------------|---------------|----------|------------|

|              | Reserved      |              |               |             |               |             |               |             | POL*          | RSPOL*     |              | FSIG*       |               | DMAC EN  | ı          |

| R, +0        |               |              |               |             |               | RV          | V, +0         | RW, +0      | F             | RW, +0     |              | RW, +000    | )             |          |            |

| 15           | 14            | 13           | 12            | 11          | 10            | 9           | 8             | 7           | 6             | 5          | 4            | 3           | 2             | 1        | 0          |

| WSYNC<br>CLR | WSYNC<br>STAT | RSYNC<br>CLR | RSYNC<br>STAT | WDROP<br>IE | WDROP<br>COND | RDROP<br>IE | RDROP<br>COND | BLOCK<br>IE | BLOCK<br>COND | LAST<br>IE | LAST<br>COND | FRAME<br>IE | FRAME<br>COND | SX<br>IE | SX<br>COND |

| RW, +0       | RW, +0        | RW, +0       | RW, +0        | RW, +0      | RW, +0        | RW, +0      | RW, +0        | RW, +1      | RW, +0        | RW,+0      | RW,+0        | RW, +0      | RW, +0        | RW,+0    | RW,+0      |

Note: \*WSPOL, RSPOL, and FSIG bit fields are not available to the C6201 and C6701 devices. These bitfields are R+0 on the C6201 and C6701 devices.

#### 4–12 Change the bit numbers (No.) of WSYNC CLR and DMAC EN in Table 4–5:

Table 4–5. DMA Channel Secondary Control Register (SECCTL) Field Descriptions (Continued)

| No.      | Field     | Description                                              | Section |

|----------|-----------|----------------------------------------------------------|---------|

| 15       | WSYNC CLR | Write synchronization status clear:                      | 4.6.1   |

|          |           | Read as 0 write 1 to clear write synchronization status. |         |

| 18 to 16 | DMAC EN   | DMA action complete pins reflect status and condition.   | 4.12    |

4–20 Add a paragraph after the introduction paragraph in section 4.6.1:

Care must be taken if software is used to poll and clear the status/conditions in the SECCTL register during a synchronized DMA transfer. To avoid inadvertently setting an extra RSYNC/WSYNC event during a synchronized DMA transfer, users should only write zeros to the STAT and CLR fields.

4–30 Change the last paragraph in section 4.8.1:

When a DMA channel is operating in split mode, only one element count and one frame count are used for both the transmit and receive transfers. The end of frame or end of block is set following the last transfer. When the channel operating in split mode is servicing a McBSP, this will normally be the last receive transfer because the transmit transfers will normally run ahead of the receive transfers. The transfer counters will be modified after the transmit transfer, so that if autoinitialization is enabled, the transfer counters may indicate that another transfer has begun before the receive portion of the split-mode transfer has completed. For split-channel operation to work properly, both the RSYNC and WSYNC fields must be set to non-zero synchronization events. Also, frame synchronization must be disabled in split-channel operation.

4–31 Change the last paragraph in section 4.8.1:

The above sequence is maintained for all transfers. However, the transmit transfers do not have to wait for all previous receive element transfers to finish before proceeding. Therefore, it is possible for the transmit stream to get ahead of the receive stream. The DMA channel transfer counter decrements (or reinitialize) after the associated transmit transfer finishes. However, reinitialization of the source address register occurs after all transmit element transfers finish. This configuration works as long as transmit transfers do not exceed eight or more transfers ahead of the receive transfers. If the transmit transfers do get ahead of the receive transfers, transmit element transfers are stopped, possibly causing synchronization events to be missed. For cases in which receive or transmit element transfers are within seven or less transfers of the other, the DMA channel maintains this information as internal status.

4–33 Change the Description of CH PRI (bits 3 to 0) in Table 4–9:

Table 4–9. DMA Auxiliary Control Register (AUXCTL) Field Descriptions

| No.    | Field  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4      | AUXPRI | Auxiliary channel priority mode                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |        | AUXPRI = 0: CPU priority<br>AUXPRI = 1: DMA priority                                                                                                                                                                                                                                                                                                                                                                                           |

| 3 to 0 | CH PRI | DMA channel priority                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        |        | CH PRI = 0000b: fixed channel priority mode auxiliary channel highest priority CH PRI = 0001b: fixed channel priority mode auxiliary channel 2nd-highest priority CH PRI = 0010b: fixed channel priority mode auxiliary channel 3rd-highest priority CH PRI = 0011b: fixed channel priority mode auxiliary channel 4th-highest priority CH PRI = 0100b: fixed channel priority mode auxiliary channel lowest priority CH PRI = other, reserved |

4–34 Change the paragraph in section 4.9.2:

A higher priority channel gains control of the DMA controller from a lower priority channel once it has received the necessary read synchronization. In switching channels, the current channel allows all data from requested reads to be completed. The DMA controller determines which higher priority channel gains control of the DMA controller read operation. That channel then starts its read operation. Simultaneously, write transfers from the previous channel are allowed to finish. The write transfer must complete before the higher priority channel will be able to start its transfer. Arbitration of the higher priority channel will occur as soon as the write from the lower priority channel completes. For example, if the lower priority channel's write is blocked by the CPU, the higher priority channel will not be able to start until the CPU releases the contending resource and the write is able to complete. This occurs even if the higher priority channel is accessing a different resource. See Chapter 5, DMA and CPU Data Access Performance, for more detail.

4–42 Add before the last paragraph in section 4.11.2.2:

As with the shared FIFO DMA, a higher priority DMA channel can still be stalled by a lower priority channel if the lower priority channel is unable to complete its write to a resource. Arbitration of the higher priority channel will occur as soon as the write from the DMA completes.

5–13 Add a new section 5.2.7:

#### 5.2.7 DMA Port Crossing

| The | e DMA has 4–6 master ports, all of which are listed below:                                                  |

|-----|-------------------------------------------------------------------------------------------------------------|

|     | Data Memory                                                                                                 |

|     | Program Memory Block 0                                                                                      |

|     | Program Memory Block 1 (on C6202/C6203 only)                                                                |

|     | XBUS I/O (on C6202/C6203/C6204 only)                                                                        |

|     | EMIF                                                                                                        |

|     | Internal Peripheral Bus (peripheral control registers including McBSP data registers)                       |

|     | e DMA auxiliary port is a slave port and should be considered a requestor ch like a programmed DMA channel. |

DMA accesses/bursts are not permitted to cross a port boundary. See section 11.3, *Memory Map*, for a listing of C620x/C670x memory map and port boundaries.

#### 6–4 Add a row to Table 6–1:

Table 6–1. Differences in TMS320C6000 EDMAs

| Features  | Supported on Device                                               | Described in Section |

|-----------|-------------------------------------------------------------------|----------------------|

| EDMA rate | Runs at CPU rate on C621x/C671x; runs at half of CPU rate on C64x | 6.1                  |

| 6-13 | Change the second | naragraph i | n section 6   | 5 |

|------|-------------------|-------------|---------------|---|

| 0-13 | Change the second | paragraphi  | 11 3001011 0. |   |

The contents of the 2K byte PaRAM, shown in Table 6–3 comprises:

- ☐ For C621x/C671x, there are 16 transfer parameter entries for the 16 EDMA events. For C64x, there are 64 transfer parameter entries for the 64 EDMA events. Each entry is six words or 24 bytes. **These areas can also serve as reload/link parameters.**

- □ Remaining parameter entries (69 entries for C621x/C671x, and 21 entries for C64x) serve as additional parameter sets used for linking transfers. Each set or entry is 24 bytes.

- 8 bytes of unused RAM that can be used as scratch pad area. Note that a part or entire EDMA RAM can be used as a scratch pad RAM provided this area corresponding to an event(s) is disabled. It is the user's responsibility to provide the transfer parameters when the event is eventually enabled.

# 6–14 Change Table 6–3:

Table 6–3. EDMA Parameter RAM Contents

| Address                  | C621x/C671x                            | C64x                              |  |  |  |  |  |  |

|--------------------------|----------------------------------------|-----------------------------------|--|--|--|--|--|--|

| 01A0 0000h to 01A0 0017h | Parameters for ev                      | rent 0 (6 words)                  |  |  |  |  |  |  |

| 01A0 0018h to 01A0 002Fh | Parameter for even                     | ent 1 (6 words)                   |  |  |  |  |  |  |

| 01A0 0030h to 01A0 0047h | Parameters for ev                      | rent 2 (6 words)                  |  |  |  |  |  |  |

| 01A0 0048h to 01A0 005Fh | Parameters for event 3 (6 words)       |                                   |  |  |  |  |  |  |

| 01A0 0060h to 01A0 0077h | Parameters for ev                      | rent 4 (6 words)                  |  |  |  |  |  |  |

| 01A0 0078h to 01A0 008Fh | Parameters for ev                      | rent 5 (6 words)                  |  |  |  |  |  |  |

| 01A0 0090h to 01A0 00A7h | Parameters for ev                      | vent 6 (6 words)                  |  |  |  |  |  |  |

| 01A0 00A8h to 01A0 00BFh | Parameters for ev                      | rent 7 (6 words)                  |  |  |  |  |  |  |

| 01A0 00C0h to 01A0 00D7h | Parameters for ev                      | rent 8 (6 words)                  |  |  |  |  |  |  |

| 01A0 00D8h to 01A0 00EFh | Parameters for ev                      | rent 9 (6 words)                  |  |  |  |  |  |  |

| 01A0 00F0h to 01A0 0107h | Parameters for even                    | ent 10 (6 words)                  |  |  |  |  |  |  |

| 01A0 0108h to 01A0 011Fh | Parameters for event 11 (6 words)      |                                   |  |  |  |  |  |  |

| 01A0 0120h to 01A0 0137h | Parameters for even                    | ent 12 (6 words)                  |  |  |  |  |  |  |

| 01A0 0138h to 01A0 014Fh | Parameters for even                    | ent 13 (6 words)                  |  |  |  |  |  |  |

| 01A0 0150h to 01A0 0167h | Parameters for even                    | ent 14 (6 words)                  |  |  |  |  |  |  |

| 01A0 0168h to 01A0 017Fh | Parameters for even                    | ent 15 (6 words)                  |  |  |  |  |  |  |

| 01A0 0180h to 01A0 0197h | Additional reload/link entry (6 words) | Parameters for event 16 (6 words) |  |  |  |  |  |  |

| 01A0 0198h to 01A0 01AFh | Additional reload/link entry (6 words) | Parameters for event 17 (6 words) |  |  |  |  |  |  |

|                          | Additional reload/link entry (6 words) |                                   |  |  |  |  |  |  |

|                          | Additional reload/link entry (6 words) |                                   |  |  |  |  |  |  |

| 01A0 05D0h to 01A0 05E7h | Additional reload/link entry (6 words) | Parameters for event 62 (6 words) |  |  |  |  |  |  |

| 01A0 05E8h to 01A0 05FFh | Additional reload/link entry (6 words) | Parameters for event 63 (6 words) |  |  |  |  |  |  |

| 01A0 0600h to 01A0 0617h | Additional reload/lin                  | ık entry (6 words)                |  |  |  |  |  |  |

| 01A0 0618h to 01A0 062Fh | Additional reload/link entry (6words)  |                                   |  |  |  |  |  |  |

|                          |                                        |                                   |  |  |  |  |  |  |

| 01A0 07E0h to 01A0 07F7h | Additional reload/lin                  | k entry (6 words)                 |  |  |  |  |  |  |

| 01A0 07F8h to 01A0 07FFh | Scratch pad ar                         | ea (2 words)                      |  |  |  |  |  |  |

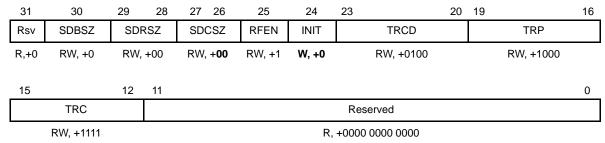

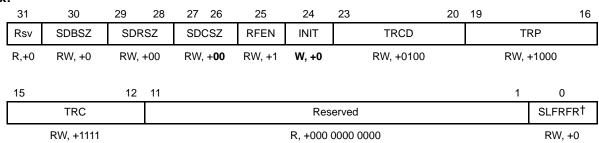

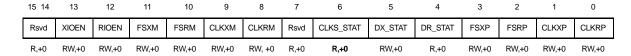

#### 6–16 Change all read/write fields and the footnote, add a footnote in Figure 6–9:

Figure 6–9. Options (OPT) Bit–Fields

| 31            |       | 29             | 28                  | 27            | 26    | 25  | 24  | 23    | 22  | 21       | 20            | 19                |       |                   | 16    |       |  |       |  |  |

|---------------|-------|----------------|---------------------|---------------|-------|-----|-----|-------|-----|----------|---------------|-------------------|-------|-------------------|-------|-------|--|-------|--|--|

|               | PRI   |                | ESIZ                | ZE            | 2DS   | SU  | М   | 2DD   | DUI | М        | TCINT         | TCC               |       |                   |       |       |  |       |  |  |

|               | RW,+x |                | RW,                 | +x            | RW,+x | RW, | ,+X | RW,+x |     | -x RW,+x |               | RW,+x RW,+x RV    |       | RW,+x RW,+x RW,+x |       | RW,+x |  | RW,+x |  |  |

| 15            | 14    | 13             | 12                  | 11            | 10    |     |     |       |     | 5        | 4             | 3                 | 2     | 1                 | 0     |       |  |       |  |  |

| rsvd <b>‡</b> | TCC   | M <sup>†</sup> | ATCINT <sup>†</sup> | rsvd <b>‡</b> |       |     | ATO | cc†   |     |          | rsvd <b>‡</b> | PDTS <sup>†</sup> | PDTD† | LINK              | FS    |       |  |       |  |  |

| RW,+x         | RW,   | +x             | RW,+x               | RW,+x         |       |     | RW  | /,+x  |     |          | RW,+x         | RW,+x             | RW,+x | RW,+x             | RW,+x |       |  |       |  |  |

<sup>†</sup> Applies to C64x only. On C621x/C671x, you should always write 0 to these reserved fields.

#### 6–17 Change the Description of ESIZE (bits 28–27) in Table 6–5:

Table 6–5. EDMA Channel Options Parameter (OPT) Description (C621x/C671x/C64x)

| Bit No. | Field | Description                                                                                      | Section |

|---------|-------|--------------------------------------------------------------------------------------------------|---------|

| 28–27   | ESIZE | Element size                                                                                     | 6.9     |

|         |       | ESIZE=00b; 32-bit word, or 64-bit doubleword (on certain C64x transfers only. See section 6.9.1) |         |

|         |       | ESIZE=01b; 16-bit half-word                                                                      |         |

|         |       | ESIZE=10b; 8-bit byte                                                                            |         |

|         |       | ESIZE=11b; reserved                                                                              |         |

#### 6–20 Change the second paragraph in section 6.6.5:

Element index provides an address offset (in bytes) to the next element in a frame. Element index is used *only* for 1D transfers. This is because 2D transfers do not allow spacing between elements, and hence the term 'array' is used to define a group of contiguous elements. Frame/array index provides an offset (in bytes) to the next frame/array in a block.

6–20 Change the title and the first paragraph in section 6.6.7:

#### 6.6.7 EDMA Performance Considerations on the C621x/C671x

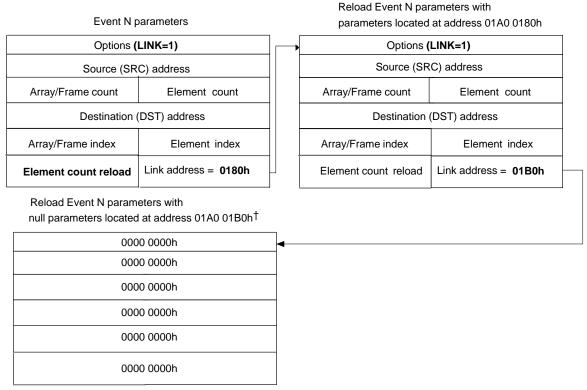

The EDMA controller provides a mechanism to link EDMA transfers. This is analogous to the autoinitialization feature in the DMA. When LINK=1 in the EDMA options parameter, the 16-bit link address specified in the EDMA parameter RAM specifies the lower 16-bit address in the parameter RAM from which the EDMA loads/reloads the parameters of the next event in the chain. Since the entire EDMA parameter RAM is located in the 01A0 xxxxh area, only the lower 16-bit address matters.

<sup>&</sup>lt;sup>‡</sup> You should always write 0 to the reserved fields.

6–24, 25 Change events on EDMA channel numbers 28, 29, 30, 31, and 53 in Table 6–8:

Table 6–8. EDMA Channel Synchronization Events – TMS320C64x

| EDMA<br>Channel<br>Number | Event Acronym | Event Description      |  |

|---------------------------|---------------|------------------------|--|

| 28                        | VCPREVT       | VCP receive interrupt  |  |

| 29                        | VCPXEVT       | VCP transmit interrupt |  |

| 30                        | TCPREVT       | TCP receive interrupt  |  |

| 31                        | TCPXEVT       | TCP transmit interrupt |  |

| 53                        | GPINT13       | GPIO event 13          |  |

- 6–32 Delete the last paragraph in section 6.9: When transferring a burst of elements to or from a 64 bit wide peripheral (e.g. L2 or EMIFA), 64-bit elements are transferred regardless of the ESIZE programmed. This allows the EDMA to maximize the available bandwidth.

- 6–32 Change the second paragraph in section 6.9.1:

When transferring a burst of elements to or from a 64-bit-wide peripheral (for example, L2 SRAM or EMIFA), 64-bit elements are transferred to maximize the available bandwidth if the element size is 32-bit word (ESIZE = 00b).

Care must be taken when performing a fixed-mode access (SUM or DUM = fixed) to peripherals that have 64-bit data paths to/from the EDMA. These include L2 SRAM, EMIFA (C64x only), and TCP/VCP (C64x only).

If the EDMA is setup with the following parameters:

- ☐ Element size is 32-bit word (ESIZE = 00b)

- Fixed address mode (SUM or DUM = 00b in the options parameter)

- ☐ Transfer/synchronization type is array-/frame-/block-synchronized (not element-synchronized, see section 6.10)

- ☐ Element count is greater than 1 (ELECNT > 1).

- ☐ Either the source or destination bus width is 64 bits.

Then the programmer must ensure that the following conditions are true:

- ☐ Element count (ELECNT) must be a multiple of 2.

- Frame/Array index field must be a multiple of 2.

Operation is undefined if the above conditions are not met.

6–32 Change the last paragraph in section 6.9.1:

For a write to a 64-bit-wide data bus with the above conditions, **both word 0 and word 1 of the fixed doubleword address are updated.** For example, **under the above conditions** a write to the L2 SRAM address 0x00000000 updates both word 0 (at address 0x00000000) and word 1 (at address 0x000000004) with the new data.

#### 6–34 Change the paragraph in section 6.10.1:

There is a special condition for reloading the element count for element synchronized (FS = 0) 1D transfers. In this case the address is updated by element size or element/frame index depending on SUM/DUM fields. See the first row in Table 6–11. Therefore, the EDMA controller keeps track of the element count to update the address. When an element sync event occurs at the end of a frame (ELECNT = 1), the EDMA controller sends off the transfer request, and reloads the ELECNT from the element count reload field in the parameter RAM. This element count reload occurs when element count is 1 and the frame count is nonzero. When configuring transfers where ELERLD will be used, ELERLD must be set to a nonzero value, or the transfer will hang. For all other types of transfers, the 16-bit element count reload field is not used because the address generation hardware (transparent to users) tracks the address directly.

6–39 Change "Elementary count reload" to "Element count reload" in Figure 6–16:

Figure 6–16. Linked EDMA Transfer

<sup>†</sup> See section 6.13 for details on null parameters

# 6–40 Change the paragraph in section 6.12:

The link address is evaluated only if LINK is equal to 1 *and* only after the event parameters have been exhausted. An event's parameters are exhausted when the EDMA controller has completed the transfer associated with the request. Table 6–13 shows the channel completion conditions when the linking of parameters is performed. There is virtually no limit to the length of linked transfers. The last transfer parameter entry should have its LINK = 1 to link to a NULL parameter set so that the linked transfer stops after the last transfer. See section 6.13 for details.

# 6–41 Change "Elementary count reload" to "Element count reload" in Figure 6–17:

Figure 6–17. Terminating EDMA Transfers

| Event N p            | parameters                  | Null parameters located at 01A0 07E0h |

|----------------------|-----------------------------|---------------------------------------|

| Options (            | LINK=1)                     | 0000 0000h                            |

| Source (SR           | C) address                  | 0000 0000h                            |

| Array/Frame count    | Element count               | 0000 0000h                            |

| Destination          | (DST) address               | 0000 0000h                            |

| Array/Frame index    | Element index               | 0000 0000h                            |

| Element count reload | Link address = <b>07E0h</b> | 0000 0000h                            |

#### 6–45 Change the TCC in Options column in Table 6–14:

Table 6–14. Transfer Complete Code (TCC) to EDMA Interrupt Mapping

| TCC<br>in Options<br>(TCINT=1) | CIPR<br>Bits Set | TCC<br>in Options<br>(TCINT=1) | CIPR Bits<br>Set |

|--------------------------------|------------------|--------------------------------|------------------|

| 0000b                          | CIP0             | 1000b                          | CIP8             |

| 0001b                          | CIP1             | 1001b                          | CIP9             |

| 0010b                          | CIP2             | 1010b                          | CIP10            |

| 0011b                          | CIP3             | 1011b                          | CIP11            |

| 0100b                          | CIP4             | 1100b                          | CIP12            |

| 0101b                          | CIP5             | 1101b                          | CIP13            |

| 0110b                          | CIP6             | 1110b                          | CIP14            |

| 0111b                          | CIP7             | 1111b                          | CIP15            |

#### 6–45 Change the TCC in Options column in Table 6–15:

Table 6–15. C64x Transfer Complete Code (TCC) to EDMA Interrupt Mapping

| TCC<br>in Options<br>(TCINT=1) | CIPRL<br>Bits Set <sup>†</sup> | TCC<br>in Options<br>(TCINT=1) | CIPRH<br>Bits Set <sup>†</sup> |

|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| 00 0000b                       | CIP0                           | 10 0000b                       | CIP32                          |

| 00 0001b                       | CIP1                           | 10 0001b                       | CIP33                          |

| 00 0010b                       | CIP2                           | 10 0010b                       | CIP34                          |

| 00 0011b                       | CIP3                           | 10 0011b                       | CIP35                          |

| 00 0100b                       | CIP4                           | 10 0100b                       | CIP36                          |

| ***                            |                                |                                |                                |

|                                |                                |                                |                                |

|                                |                                |                                |                                |

| 01 1110b                       | CIP30                          | 11 1110b                       | CIP62                          |

| 01 1111b                       | CIP31                          | 11 1111b                       | CIP63                          |

#### 6–48 Change the second paragraph in section 6.15.1:

To enable the EDMA controller to chain channels by way of a single event, the TCINT bit must be set to '1'. Additionally, the relevant bit in the channel chain enable register (CCER) in Figure 6–20 should be set to trigger off the next channel transfer specified by TCC. Since events 8 to 11 are the only EDMA channels that support chaining, only these bits are implemented in CCER. Reading unused bits returns **the corresponding bits in the EER** and writing to them has no effect. Therefore, one can still specify a TCC value between 8 and 11, and need not necessarily initiate the transfer on channels 8-11. However, the event is still captured in the ER[11:8] even if the corresponding bit in CCER is disabled. This allows selective enabling and disabling of these four specific events.

#### 6–48 Change the paragraph in section 6.15.2:

The C64x EDMA transfer chaining is an expansion of the C621x/C671x transfer chaining. Any of the 64 transfer completion codes of the C64x EDMA can be used to trigger another channel transfer. The user-specified transfer complete code is expanded to a 6-bit value TCCM:TCC. The 4 bits in the TCC field (bits 19 to 16) of the options parameter are the least significant bits of the transfer complete code, while the new TCCM bit fields are the most significant bits of the transfer complete code. For example, if the transfer complete code (TCCM:TCC) is 010001b (i.e. TCCM = 01, TCC = 0001b) and CCERL[17] = 1 is specified for EDMA channel 4, the completion of the channel 4 transfer will initiate the next transfer specified by EDMA channel 17, provided that the channel 4 TCINT = 1. **Unlike the C621x/C671x**, the event bits on the C64x are captured in the ER *only* if the corresponding bits in CCER are enabled.

6–55 Change the C64x Requesters column in Table 6–16:

Table 6-16. Programmable Priority Levels for Data Requests

| PRI(31:29) | C621x/C671x<br>Priority Level | C621x/C671x<br>Requestors | C64x Priority Level      | C64x Requesters                                        |

|------------|-------------------------------|---------------------------|--------------------------|--------------------------------------------------------|

| 000b       | Level0; urgent priority       | L2 controller             | Level0; urgent priority  | L2 controller, EDMA, QDMA, <b>HPI</b> , and <b>PCI</b> |

| 001b       | Level1; high priority         | EDMA, QDMA<br>and/or HPI  | Level1; high priority    | L2 controller, EDMA, QDMA, <b>HPI</b> , and <b>PCI</b> |

| 010b       | Level2; low priority          | EDMA, QDMA                | Level 2; medium priority | L2 controller, EDMA, QDMA, <b>HPI</b> , and <b>PCI</b> |

| 011b       | Reserved                      | Reserved                  | Level 3, low priority    | L2 controller, EDMA, QDMA, <b>HPI</b> , and <b>PCI</b> |

| 100b –111b | Reserved                      | Reserved                  | Reserved                 | Reserved                                               |

#### 6–55 Change the paragraph in section 6.17.1:

The priority queue status register (PQSR) shown in Figure 6–24 (C621x/C671x) and Figure 6–25 (C64x) indicates whether the transfer request queue is empty on the priority level queues. Status bits PQ in the PQSR provide the status of the queues. A '1' in the PQ bit indicates that there are no requests pending in the respective priority level queue. For C621x/C671x, if PQSR[0] is '1', this means all L2 requests for data movement have been completed and there are no requests pending in the priority level 0 queue. For C64x, if PQSR[0] is '1', this means all requests for data movement from requestors programmed for priority level 0 have been completed.

6–56 Add a paragraph after the section header in section 6.17.2:

#### 6.17.2 Transfer Request Queue Length

Care should be taken to not overload any priority queue, as overloading any one queue can adversely affect all queues. When a transfer is submitted to a queue that is full, the EDMA controller stalls until room in the queue is available. While stalled, the EDMA controller does not process any other events, including those events that submit requests on a different priority queue. Events are still captured in the ER and processed when the EDMA controller is released.

#### 6–57 Change Table 6–18:

Table 6–18. Transfer Request Queues (C64x)†

| Queue | Priority Level<br>(PRI) | Total<br>Queue<br>Length<br>(fixed) | Requester              | Default<br>Queue<br>Length | Register to Program<br>Queue Length |

|-------|-------------------------|-------------------------------------|------------------------|----------------------------|-------------------------------------|

| Q0    | 0; urgent priority      | 16                                  | L2 controller and QDMA | 6                          | L2ALLOC0                            |

|       |                         |                                     | EDMA                   | 2                          | PQAR0                               |

|       |                         |                                     | HPI/PCI                | 0                          | TRCTL/TRCTL                         |

| Q1    | 1; high priority        | 16                                  | L2 controller and QDMA | 2                          | L2ALLOC1                            |

|       |                         |                                     | EDMA                   | 6                          | PQAR1                               |

|       |                         |                                     | HPI/PCI                | 0                          | TRCTL/TRCTL                         |

| Q2    | 2; medium priority      | 16                                  | L2 controller and QDMA | 2                          | L2ALLOC2                            |

|       |                         |                                     | EDMA                   | 2                          | PQAR2                               |

|       |                         |                                     | HPI/PCI                | 4                          | TRCTL/TRCTL                         |

| Q3    | 3; low priority         | 16                                  | L2 controller and QDMA | 2                          | L2ALLOC3                            |

|       |                         |                                     | EDMA                   | 6                          | PQAR3                               |

|       |                         |                                     | HPI/PCI                | 0                          | TRCTL/TRCTL                         |

<sup>†</sup>L2 controller and QDMA share one queue allocation. L2ALLOCx register controls this queue allocation length. HPI and PCI share one queue allocation.

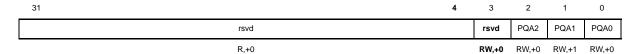

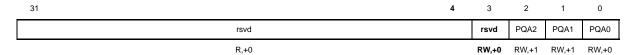

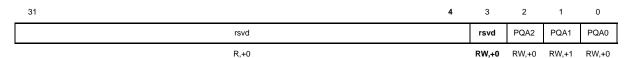

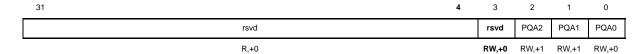

#### 6–58 Change Figures 6-26, 6-27, 6-28, and 6-29:

Figure 6–26. Priority Queue Allocation Register 0 (PQAR0) (C64x only)

Figure 6–27. Priority Queue Allocation Register 1 (PQAR1) (C64x only)

Figure 6–28. Priority Queue Allocation Register 2 (PQAR2) (C64x only)

TRCTL register in the HPI module controls the queue allocation length of HPI requests.

TRCTL register in the PCI module controls the queue allocation length of PCI requests.

Figure 6–29. Priority Queue Allocation Register 3 (PQAR3) (C64x only)

6–59 Change the first bullet in section 6.18:

☐ EDMA stalls occur when the EDMA submits another request to a priority level queue that is already full.

6–59 Add the following text after the bullets in section 6.18:

EDMA bandwidth is fully utilized when performing burst transfer, which is obtained if and only if the EDMA transfer is configured as:

- ☐ Transfer/synchronization type is array-/frame-/block-synchronized transfer (not element-synchronized, see section 6.10).

- ☐ Element size is 32-bit (ESIZE = 00b)

- $\square$  Addressing mode is increment, decrement, or fixed (SUM or DUM = 00/01/10b in the options parameter)

The EDMA will perform single element transfers for all transfers not meeting all of the above conditions, which will utilize only a portion of the bandwidth available.

For burst transfer types described above, the burst length is dictated by the 1D component of the transfer, which is specified by the ELECNT field. For array-or frame-synchronized transfer, the 1D component of the transfer is the amount of data that gets transferred per synchronization event. For block-synchronized transfers, the complete 2D transfer is transferred per synchronization event; however, burst transfers are only performed for the 1D component. If the 1D length (ELECNT) is programmed to a small value, the performance will reduce accordingly and in the worst case (ELECNT = 1), the performance will be identical to the performance described for single element transfers.

#### 6–61 Change Figure 6–32:

Figure 6–32. QDMA Options Register (QDMA\_OPT, QDMA\_S\_OPT)

| _ | 31 29 | 28 27 | 26    | 25 24 | 23    | 22 21 | 20    | 19 16 | 15   | 14 13 | 12 1 | 0    |

|---|-------|-------|-------|-------|-------|-------|-------|-------|------|-------|------|------|

|   | PRI   | ESIZE | 2DS   | SUM   | 2DD   | DUM   | TCINT | TCC   | Rsvd | TCCM  | Rsvd | FS   |

|   | W, +0 | W,+0 | W,+0  | W,+0 | W,+0 |

Notes: 1) TCCM applies to C64x only. For C621x/C671x, this bit is Reserved W,+0.

2) Register QDMA\_OPT is read/writable. Pseudo-register QDMA\_S\_OPT is write only.

6–62 Change the first paragraph in section 6.19.5:

The QDMA has several stalling conditions. Once a write has been performed to one of the pseudo-registers (resulting in a pending QDMA transfer request), future writes to the QDMA registers are stalled until the transfer request is sent. Normally this will occur for 2–3 EDMA cycles, as this is how long it takes to submit a transfer. Stalls are not generally seen by the CPU, because writes to QDMA registers occur via the L1D write buffer. Future writes to the buffer may eventually fill it up and stall the CPU from subsequent reads/ writes.

6–62 Change the third paragraph in section 6.19.5:

Similar to the EDMA channels, QDMA can have programmable priority in the lower levels as described in section 6.17. The PRI bit-field in the QDMA\_OPT register specifies the priority level of the QDMA. On the C621x/C671x, level 0 (urgent priority) is reserved for L2 cache accesses; thus, QDMA requests with level 0 or reserved values will be discarded.

6–66 Change the first paragraph in section 6.21.1.1:

For TMS320C64x, cache servicing requests can be made on any priority levels as specified in the P bits in the CCFG register. For read requests, the cache controller always requests an L2 line in two bursts of 64 bytes each, requesting the "missed" portion of the line first. For write requests, as a result of flush/clean operations or eviction, the cache controller transfers one complete L2 line in two bursts of **64 bytes** each.

6–66 Change the paragraph in section 6.21.1.2:

The HPI/PCI automatically generates transfer requests to service host activity. For C621x/C671x, these transfer request submissions are submitted only with a high priority and are invisible to the user. For C64x, by default HPI/PCI transfer requests are submitted with medium priority, but request priority can be programmed to any of the four priority levels by setting the PRI field in the TRCTL register to the appropriate value. The HPI/PCI submits a transfer request for a single element read or write for fixed mode host accesses and a transfer request for a short data burst for autoincrement transfers. The burst size is always for eight or fewer elements. See section 6.17 for available HPI transfer request priority.

6–66 Change the paragraph in section 6.21.1.3:

The EDMA channel transfers can be submitted with **urgent (C64x only)**, high, medium (C64x only), or low priority; with the recommendation that high priority be reserved for short bursts and single element transfers and low priority be used for longer (background) block moves. It is also recommended that transfers be divided between the priority levels when applicable, as this helps to maximize the device performance.

6–73 Change the fourth paragraph in section 6.22.3:

For this example it is assumed that the 16-bit data is located in external RAM, beginning at address 0xA0000000 (CE2). The QDMA is used to bring four frames of 1k half-words from their locations in RAM to internal data memory beginning at 0x00002000. The index value required is ELEIDX = F x S = 4 x 2 = 8.

7–3 Add a paragraph below Figure 7–2 in section 7.1:

Through the HPI, an external host is capable of accessing the entire DSP memory map *except* the following:

- ☐ L2 control registers (C6x1x only)

- ☐ Interrupt selector registers

- ☐ Emulation logic

7–21 Add a paragraph at the end of section 7.4.3:

When performing reads with autoincrement, the C64x differs slightly from the C621x/C671x in that the C64x will not indicate ready (HRDY low) until the internal read buffer has filled with the 16-word prefetch. Thus, accesses to slow regions of memory, such as internal peripheral registers or slow external memory, might take a significant amount of time. For best performance, accesses to these regions should be done in fixed mode unless multiple words are desired.

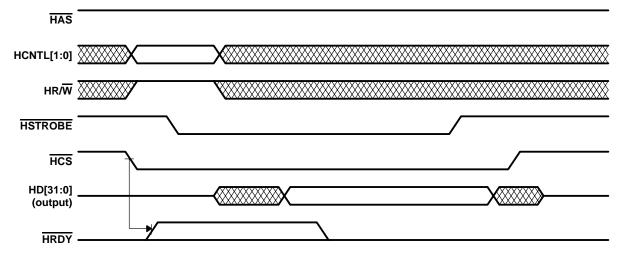

7–22 Change Figure 7–11 (delete HRDY case 2 waveform):

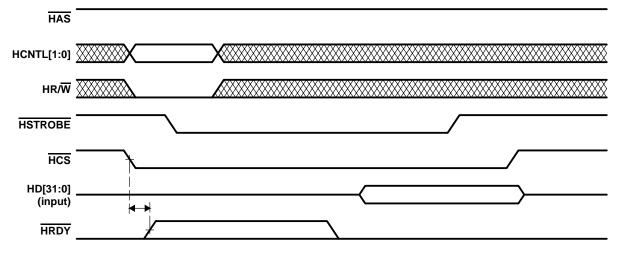

Figures 7–11. HPI32 Read Timing (HAS Not Used, Tied High) for C64x only

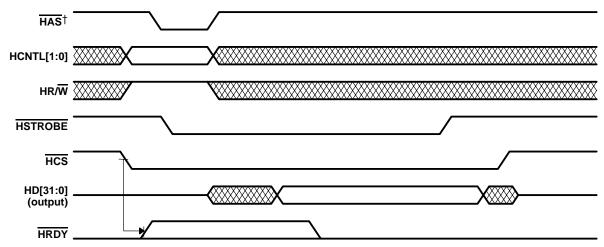

7–22 Change Figure 7–12 (delete HRDY case 2 waveform):

Figures 7–12. HPI32 Read Timing (HAS Used) for C64x only

<sup>†</sup> For correct operation, strobe the HAS signal only once per HSTROBE cycle.

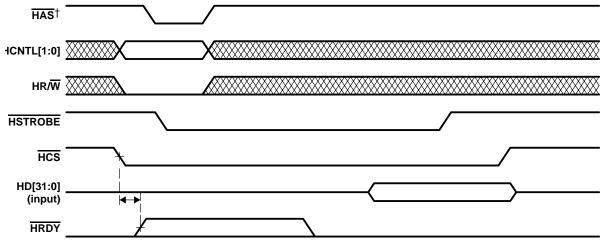

# 7–23 Change the $HR/\overline{W}$ and $\overline{HRDY}$ waveforms in Figure 7–13:

Figure 7–13. HPI Write Timing (HAS Not Used, Tied High) for C64x only

7–23 Change the HR/W and HRDY waveforms in Figure 7–14:

Figure 7–14. HPI Write Timing (HAS Used) for C64x only

<sup>†</sup> For correct operation, strobe the HAS signal only once per HSTROBE cycle.

#### 7–24 Add a row to Table 7–7:

Table 7–7. HPI Registers for C64x

| Register<br>Abbreviation | Register<br>Name | Host<br>Read/Write<br>Access | CPU<br>Read/Write<br>Access | CPU Read/Write<br>(Hex Byte<br>Address) |

|--------------------------|------------------|------------------------------|-----------------------------|-----------------------------------------|

| TRCTL                    | TR control       | _                            | RW                          | 018A 0000h                              |

# 7–25 Change the first paragraph in section 7.5.1:

The HPIA contains the address of the memory accessed by the HPI at which the current access occurs. This address is a 32-bit word address with all 32-bits readable/writable. The two LSBs always function as 0, regardless of the value read from their location. The C62x/C67x HPIA register is only accessible by the host. It is not mapped to the DSP memory.

#### 7–25 Change the second paragraph in section 7.5.1:

The C64x HPIA register is accessible by both the host and the CPU. Furthermore, the HPIA register is separated into two registers internally: the HPI address write register (HPIAW), and the HPI address read register (HPIAR). By separating the HPIA into HPIAW and HPIAR internally, the CPU can update the read and write memory address independently to allow the host to perform read and write to different address ranges. When reading HPIA from the CPU, the value returned corresponds to the address currently being used by the HPI and DMA to transfer data inside the DSP. It is not the address for the current transfer at the external pins. Thus, reading HPIA does not indicate the status of a transfer, and should not be relied upon to do so.

#### 7–25 Change the paragraph in section 7.5.2:

The HPIC register, shown in Figure 7–15 and Figure 7–16 and summarized in Table 7–8, is normally the first register accessed to set configuration bits and initialize the interface. From the host's view, the HPIC is organized as a 32-bit register with two identical halves, meaning the high halfword and low halfword contents are the same. On a host write, both halfwords must be identical, except when writing the DSPINT bits in HPI16 mode (see section 7.5.4). In HPI16 mode when setting DSPINT = 1, the host must only write '1' to the lower 16-bit halfword or upper 16-bit halfword, but not both. In HPI32 mode, the upper and lower halfwords must always be identical. From the C6000 (CPU) view, the HPIC is a 32-bit register with only 16-bits of useful data. Only CPU writes to the lower halfword affect HPIC value and HPI operation.

#### 7–25 Add a second paragraph in section 7.5.2:

On C64x, the HWOB bit is writable by the CPU. Therefore, care must be taken when writing to the HPIC, in order not to write an undesired value to HWOB.

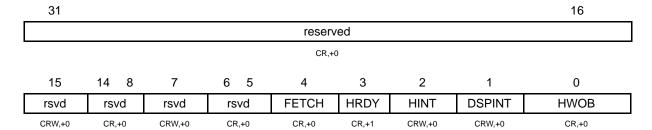

7–26 Change the title, all read/write fields, and the footnote in Figure 7–15:

Figure 7-15. HPIC Register—Host Reference View

|   | 31                | 30 24 | 23     | 22 21 | 20     | 19    | 18     | 17     | 16                                  |

|---|-------------------|-------|--------|-------|--------|-------|--------|--------|-------------------------------------|

|   | rsvd <sup>†</sup> | rsvd  | rsvd†  | rsvd  | FETCH  | HRDY  | HINT   | DSPINT | HWOB                                |

|   | HRW,+0            | HR,+0 | HRW,+0 | HR,+0 | HRW,+0 | HR,+1 | HRW,+0 | HRW,+0 | HRW,+0 (C62x/C67x)<br>HRW,+0 (C64x) |

|   | 15                | 14 8  | 7      | 6 5   | 4      | 3     | 2      | 1      | 0                                   |

|   | rsvd†             | rsvd  | rsvd†  | rsvd  | FETCH  | HRDY  | HINT   | DSPINT | HWOB                                |

| _ | HRW,+0            | HR,+0 | HRW,+0 | HR,+0 | HRW,+0 | HR,+1 | HR,+0  | HRW,+0 | HRW,+0 (C62x/C67x)<br>HRW,+0 (C64x) |

<sup>†</sup> For C62x/C67x, bits 7, 15, 23, 31 are read-only; **HR,+0**. For C64x, bits 7, 15, 23, and 31 are writable fields and must be written with 0. Otherwise, operation is undefined.

#### 7–26 Add a new Figure 7–16. The subsequent figures are renumbered accordingly:

Figure 7–16. HPIC Register—C6000 Reference View

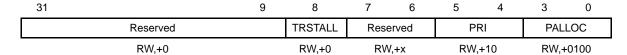

7–26 Add a new section 7.5.3, Figure 7–17, and Table 7–9. The subsequent sections, figures, and tables are renumbered accordingly:

# 7.5.3 TR Control Register (TRCTL) (C64x only)

The TR control register (TRCTL) controls how the HPI submits its requests to the EDMA subsystem. The TRCTL is shown in Figure 7–17 and summarized in Table 7–9.

Figure 7–17. TR Control Register (TRCTL)

Table 7–9. TR Control Register (TRCTL) Bit Descriptions

| Bit     | Description                                                                                                                                                                                                                   | Section |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| PALLOC  | Controls the total number of outstanding requests that can be submitted by the HPI to the EDMA                                                                                                                                | 7.5.3   |

| PRI     | Controls the priority queue level that HPI requests are submitted to.                                                                                                                                                         | 7.5.3   |

| TRSTALL | Forces the HPI to stall all HPI requests to EDMA This bit allows safe changing of the PALLOC and PRI fields. TRSTALL=0: Allows HPI requests to be submitted to EDMA TRSTALL=1: Halts the creation of new HPI requests to EDMA | 7.5.3   |

To safely change the PALLOC or PRI bits in TRCTL, the TRSTALL bit needs to be used to ensure a proper transition. The following procedure must be followed to change the PALLOC or PRI bits:

- Set the TRSTALL bit to 1 to stop the HPI from submitting TR requests on the current PRI level. In the same write, the desired new PALLOC and PRI fields may be specified.

- Clear all EDMA event enables (EER) corresponding to both old and new PRI levels to stop EDMA from submitting TR requests on both PRI levels.

Do not manually submit additional events via the EDMA.

- 3) Do not submit new QDMA requests on either old or new PRI level.

- 4) Stop L2 cache misses on either old or new PRI level. This can be done by forcing program execution or data accesses in internal memory. Another way is to have the CPU executing a tight loop that does not cause additional cache misses.

- 5) Poll the appropriate PQ bits in PQSR until both queues are empty (see section 6.17.1).

- 6) Clear the TRSTALL bit to 0 to allow the HPI to continue normal operation.

Requestors are halted on the old HPI PRI level so that memory ordering can be preserved. In this case, all pending requests corresponding to the old PRI level must be let to complete before HPI is released from stall state.

Requestors are halted on the new PRI level to ensure that at no time can the sum of all requestor allocations exceed the queue length. By halting all requestors at a given level, the user can be free to modify the queue allocation counters of each requestor.

#### 7–27 Change the paragraph in section 7.5.4:

The host can interrupt the CPU by writing to one of the DSPINT bits in the HPIC. In order for the CPU to receive DSPINT correctly, the host must only write one but not both of the DSPINT bits in HPIC register. The DSPINT bit is tied directly to the internal DSPINT signal. By writing DSPINT = 1 when DSPINT = 0, the host causes a low-to-high transition on the DSPINT signal. If the user programs the selection of the DSPINT interrupt with interrupt selector, the CPU detects the transition of DSPINT as an interrupt condition. Unlike a host write, a CPU write of DSPINT = 1 when DSPINT = 0 has no effect. The CPU can clear the DSPINT bits by writing a 1 to DSPINT when DSPINT = 1. Writing DSPINT = 0 (in HPIC) via the host or the CPU does not affect either the DSPINT bit or signal in any case.

#### 7–27 Change the first paragraph in section 7.5.5:

The CPU can send an active interrupt condition on the  $\overline{HINT}$  signal by writing to the HINT bit in the HPIC. The HINT bit is inverted and tied directly to the  $\overline{HINT}$  pin. The CPU can set  $\overline{HINT}$  active by writing HINT = 1. The host can clear the  $\overline{HINT}$  to inactive by writing a 1 to HINT. Writing HINT = 0 (in HPIC) via the host or the CPU does not affect either the HINT bit or the  $\overline{HINT}$  signal.

#### 7–32 Change the Value During Access column in Table 7–14:

Table 7–14. Data Read Access in Fixed Address Mode for HPI32

|                                | 1        | Value Dur | ing Access | Value After Access |          |          |          |

|--------------------------------|----------|-----------|------------|--------------------|----------|----------|----------|

| Event                          | HD       | HR/W      | HCNTL[1:0] | HRDY               | HPIC     | HPIA     | HPID     |

| Host reads HPIC Data not ready | ???????? | 1         | 00         | 1                  | 00000000 | 80001234 | ???????? |

| Host writes HPID<br>Data ready | 789ABCDE | 0         | 11         | 0                  | 00080008 | 80001234 | 789ABCDE |

**Note:** The "?" in this table indicate the value is unknown.

# 7–35 Change the title of Tables 7–18 and 7–19:

Table 7–18 16-Bit Data Write Access to HPI in Fixed Address Mode: HWOB = 1

Table 7–19. 16-Bit Data Write Access to HPI in Fixed Address Mode: HWOB = 0<sup>t</sup>

7–35 Add a new table after Table 7–19. The subsequent tables are renumbered accordingly:

Table 7–20. 32-Bit Data Write Access to HPI in Fixed Address Mode: HWOB = 1

|                                         |      |          | Value D | uring Access | Va   | lue After Acc | ess      | - Location |          |          |

|-----------------------------------------|------|----------|---------|--------------|------|---------------|----------|------------|----------|----------|

| Event                                   | HD   | HBE[1:0] | HR/W    | HCNTL[1:0]   | HRDY | HHWIL         | HPIC     | HPIA       | HPID     | 80001234 |

| Host writes HPID<br>1st halfword        | 5566 | 00       | 0       | 11           | 1    | 0             | 00010001 | 80001234   | ???????? | 00000000 |

| Waiting for previous access to complete |      |          |         |              |      |               |          |            |          |          |

| Host writes HPID<br>1st halfword        | 5566 | 00       | 0       | 11           | 0    | 0             | 00090009 | 80001234   | ????5566 | 00000000 |

| Host writes HPID<br>2nd halfword        | wxyz | 00       | 0       | 11           | 0    | 1             | 00090009 | 80001234   | wxyz5566 | 00000000 |

| Waiting for access to complete          | ???? | ??       | ?       | ??           | 1    | ?             | 00010001 | 80001234   | wxyz5566 | wxyz5566 |

<sup>†</sup> For C620x/C670x HPI, wxyz represents a "don't care" value on the HD pins. The HBE[1:0] value indicates that only 16-bit is transferred. For C621x/C671x and C64x HPI, however, wxyz should be 0000 on the HD pins. The entire 32-bit word is transferred.

Note: The "?" in this table indicate the value is unknown.

### 7–41 Change the paragraph in section 7.7:

All C621x/C671x HPI transfers are placed in the high priority transfer queue, Q1. **All C64x HPI transfers can be programmed to any of the four priority levels, with the medium priority level set as default**. Refer to section 6.17, *Resource Arbitration and Priority Processing*, for details on transfer priority.

#### 8–6 Add a footnote in Table 8–2 at the XHOLD and XHOLDA signals:

Table 8–2. Signal State for Disabled Host Port

| XBUS Signal         | I/O Port Mode<br>(I/O/Z) | External<br>Connection |  |

|---------------------|--------------------------|------------------------|--|

| XHOLD†              | I/O/Z                    | Pull down              |  |

| XHOLDA <sup>†</sup> | I/O/Z                    | Pull down              |  |

<sup>†</sup> Internal arbitration should be enabled, such that the DSP is the master of the bus when not using the host port. See section 8.6 for more details.

#### 8–9 Change the Description of XFRAT in Table 8–5:

Table 8–5. Expansion Bus Global Control Register (XBGC) Field Description

| Field | Description                                                                                                                                         | Section |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| XFRAT | FIFO clock rate                                                                                                                                     | 8.4.2   |

|       | XFRAT = 00: XFCLK = 1/8 CPU clock rate                                                                                                              |         |

|       | XFRAT = 01: XFCLK = 1/6 CPU clock rate                                                                                                              |         |

|       | XFRAT = 10: XFCLK = 1/4 CPU clock rate                                                                                                              |         |

|       | XFRAT = 11: XFCLK = 1/2 CPU clock rate                                                                                                              |         |

|       | The FIFO clock setting cannot be changed while a DMA request to XCE space is active.                                                                |         |

|       | The XFCLK should be disabled before changing XFRAT field. There is no delay required between enabling/disabling XFCLK and changing the XFRAT field. |         |

#### 8–12 Add a paragraph in section 8.4:

Figure 8–5 illustrates how to interface four 8-bit FIFOs to the I/O port (memory map for this case is described in Table 8–8). Figure 8–6 is an example of an interface between two 16-bit FIFOs and the I/O port.

The XOE, XRE, XWE, and XCEn signals are not tri-stated while the DSP releases control of the XBUS.

8–14 Add a paragraph below the Notes in section 8.4.1:

An access to a section of memory that does not return a ready indication is not allowed. This includes accesses to XBUS I/O asynchronous spaces with XRDY pulled inactive or left floating on the device. Possible requestors are: programmed DMA channels or HPI/PCI/XBUS host mastering via the auxiliary DMA. This type of access can create a stall indefinitely.

- 8–14 Delete the third paragraph in section 8.4.2: The XOE, XRE, XWE, and XCEn signals are not tri-stated while the DSP releases control of the XBUS.

- 8–24 Change the last paragraph in section 8.5.1.2:

This register is used when the host port operates either in synchronous or asynchronous mode. The DSP does not have access to the XBISA register content. Burst transfers in the synchronous host-port mode are always expected to occur with autoincrement (AINC bit should be **cleared to 0**). In autoincrement mode (AINC = 0), operation is undefined if an external host attempts to access the last 2 word locations in the **internal program/data RAM**. This is because the DSP tries to prefetch data from reserved locations. Operation is also undefined if an external host attempts to cross a block boundary in a single DMA transfer. See Chapter 2 for details.

8–26 Change the Descriptions of DSPINT and INTSRC in Table 8–16:

Table 8–16. Expansion Bus Host Port Interface Control Register (XBHC) Description

| Field  | Description                                                                                                                                                                                                         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSPINT | The expansion bus to DSP interrupt (set either by the external host or the completion of a master transfer) is cleared when this bit is set. The DSPINT bit must be manually cleared before another one can be set. |

| INTSRC | The XBUS host port interrupt can be caused either by DSPINT bit or by XFRCT counter. The INTSRC selects interrupt source between DSPINT and XFRCT counter.                                                          |

|        | INTSRC=0: interrupt source is DSPINT bit of the XBISA. When a zero is written to INTSRC, the DSPINT of the XBISA is copied to the DSPINT bit of the XBHC.                                                           |

|        | INTSRC=1: interrupt is generated at the completion of the master transfer initiated by writing to the START bit-field.                                                                                              |

8–36 Add a paragraph before the third paragraph in section 8.5.2.2:

Initial access made to the expansion bus in host slave mode should be done in the order indicated above. After reset, the first access from the host should be an XBISA write followed by an XBD read/write. Undefined operation may occur if an XBISA read or an XBD read/write occurs before an XBISA write.

To read/write from the DSP memory space, the host must follow the following sequence:

8–38 Change Figure 8–22 to show the XRDY signal in high impedance (*not* high) in clock cycle four and five. The DSP should start driving the XRDY signal during the sixth clock cycle.

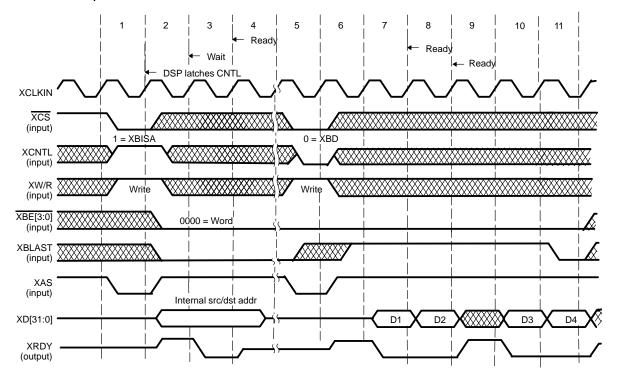

Figure 8-22. Expansion Bus Master Writes a Burst of Data to the DSP

8–40 Change Figure 8–23 to show the XRDY signal in high impedance (*not* high) in clock cycle four and five. The DSP should start driving the XRDY signal during the sixth clock cycle.

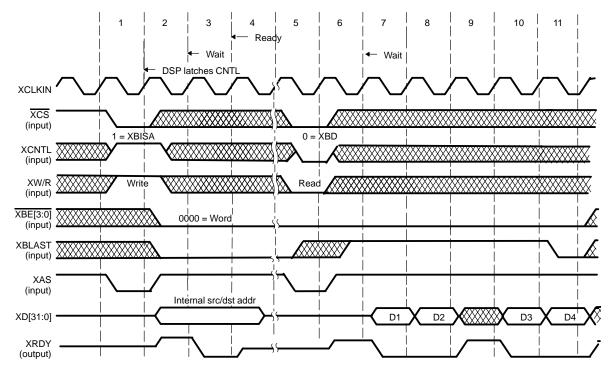

Figure 8-23. The Bus Master Reads a Burst of Data From the DSP

#### 8–43 Add a paragraph before the third paragraph in section 8.5.3:

Initial access made to the expansion bus in host slave mode should be done in the order indicated above. After reset, the first access from the host should be an XBISA write followed by an XBD read/write. Undefined operation may occur if an XBISA read or an XBD read/write occurs before an XBISA write.

If the XBUS host port is configured to operate in asynchronous mode, the  $\overline{XCS}$  signal is used for four purposes:

#### 8–43 Change the fourth paragraph in section 8.5.3:

The XRDY signal of the DSP functions differently than the C6201 HPI READY signal. The XRDY signal indicates normally not ready condition (active low READY signal is internally OR-ed with  $\overline{\text{XCS}}$  signal in order to obtain XRDY). **XRDY should be polled during reads/writes to/from the XBISA or XBD.**

#### 8–44 Add a new section 8.5.4:

#### 8.5.4 Special Circumstance of XBUS Host Memory Accesses

When the XBUS host port executes a read from the DSPs memory space, it does so by performing burst prefetches of 3 words. This results in the DMA auxiliary channel reading 3 higher-word addresses that you may not have explicitly requested. This occurs only under the following situations:

| An external master performs an autoincremented read from the XBUS configured for host slave mode (both synchronous or asynchronous). |

|--------------------------------------------------------------------------------------------------------------------------------------|

| The XBUS configured as the master in synchronous host port mode writes from the DSP to the external space via the XBUS.              |

The accesses described above can cause the following undesired operations:

- 1) Accesses to undesired CE spaces:

- When reading the top 3 words of EMIF CE0, the resulting prefetches can cause an inadvertent access to CE1 that may cause an undesired read to a device or a stall if the inadvertent access is to an asynchronous memory space with ARDY left floating or pulled inactive (notready).

- The above example also applies to CE2 with the resulting prefetches possibly causing an inadvertent access to CE3 (see section 11.3, *Memory Map*).

Associated design tip: If not using ARDY or XRDY, always pull to the ready state to avoid stalls. If you always want to detect bad software setups, always pull to the not-ready state to detect system stalls.

- 2) Unintended port crossings or illegal accesses to a reserved location:

- When reading the top 3 words of EMIF CE1, the access can cross into either program memory (PMEM) block 0 when in Map 0 or to the internal peripheral bus (PBus) region storing EMIF control registers when in Map 1. This is an illegal port crossing.

- When reading the top 3 words of EMIF CE3, the access can cross into reserved address space. This is an illegal access.

- When reading the top 3 words of PMEM block 0, the access can cross into PMEM block 1. This is an illegal port crossing.

- When reading the top 3 words of PMEM block 1, the access can cross into reserved address space. This is an illegal access.

- When reading the top 3 words of data memory (DMEM) block 1, the access can cross into reserved address space. This is an illegal access.

- When reading anywhere in the PBus space, you may prefetch ahead to three undesired control registers. This can cause an illegal access when accessing a reserved register address. If the register access has side effects (like reading the McBSP DRR, clearing RRDY), then you may inadvertently cause these side effects.

Note: A restriction does NOT exist when crossing between DMEM block 0 and block 1 because they both use the same DMA port.

Associated design tips:

- When reading internal peripheral registers:

- For reads from an external master, use fixed-mode addressing. As a broader statement, it is good practice to use fixed mode also when writing to peripheral registers as sometimes there are gaps between them.

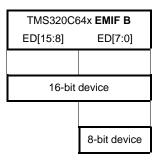

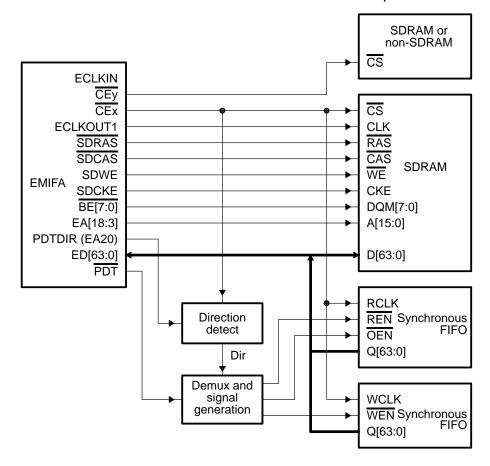

- Do not use the XBUS host port configured in synchronous master mode to directly copy peripheral register values to external slaves. This is an atypical operation. If you must do so, copy the register data to an internal space with the CPU and then copy those internal locations to external space.