# TMS320C6000 Peripherals Reference Guide

Literature Number: SPRU190C April 1999

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1999, Texas Instruments Incorporated

### Preface

## **Read This First**

### About This Manual

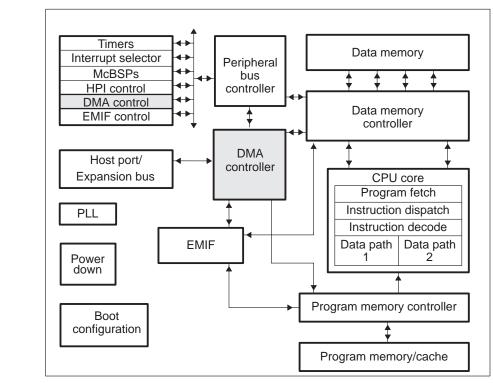

This reference guide describes the on-chip peripherals of the TMS320C6000 digital signal processors (DSPs). Main topics are the program memory, the data memory, the direct memory access (DMA) controller, the enhanced DMA controller (EDMA), the host-port interface (HPI), the exansion bus, the external memory interface (EMIF), the boot configuration, the multichannel buffered serial ports (McBSPs), the timers, the interrupt selector and external interrupts, and the power-down modes.

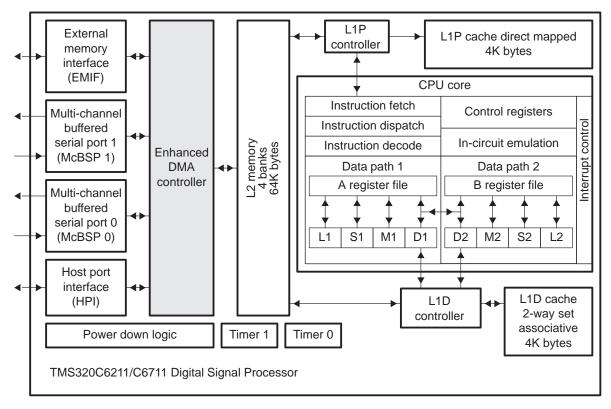

The TMS320C62x ('C62x) and the TMS320C67x ('C67x) generations of digital signal processors make up the TMS320C6000 platform of the TMS320 family of digital signal processors. The 'C62x devices are fixed-point DSPs, and the 'C67x devices are floating-point DSPs. The TMS320C6000 ('C6000) is the first DSP to use the VelociTI<sup>™</sup> architecture, a high-performance, advanced VLIW (very long instruction word) architecture. The VelocTI architechure makes the 'C6x an excellent choice for multichannel, multifunction, and high data rate applications.

#### Notational Conventions

This document uses the following conventions:

Program listings, program examples, names are shown in a special font. Here is a sample program listing:

| *A0,A1   |

|----------|

| A1,A2,A3 |

| 3        |

| A1,A4,A5 |

|          |

☐ Throughout this book MSB means *most significant bit,* and LSB means *least significant bit.*

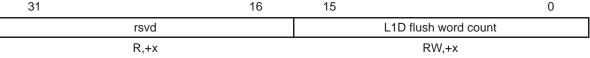

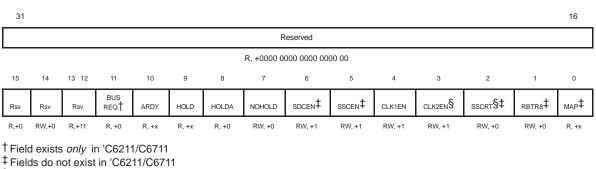

Registers are described throughout this book in register diagrams. Each diagram shows a rectangle divided into fields that represent the fields of the register. Each field is labeled with its name inside, its beginning and ending bit numbers above, and its properties below. A legend explains the notation used for the properties. For example:

| 31     | 25 | 24  | 23   | 22  | 21  | 20 |       | 18 | 17  | 16            |

|--------|----|-----|------|-----|-----|----|-------|----|-----|---------------|

| FIELDA |    | FIE | LDB  | FIE | LDC |    | R, +1 |    | RW  | ′, <b>+</b> 0 |

| RW, +0 |    | RC  | , +x | R,  | +0  |    | R, +1 |    | HRV | V, +0         |

**Note:** R = Readable by the CPU, W = Writeable by the CPU, +x = Value undefined after reset, +0 = Value is 0 after reset, +1 = Value is 1 after reset, C = Clearable by the CPU, H = reads/writes performed by the host

#### **Related Documentation From Texas Instruments**

The following documents describe the TMS320C6x family and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

- **TMS320C6000 Technical Brief** (literature number SPRU197) gives an introduction to the 'C6000 platform of digital signal processors, development tools, and third-party support.

- **TMS320C6000 CPU and Instruction Set Reference Guide** (literature number SPRU189) describes the 'C6000 CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

- **TMS320C6000 Programmer's Guide** (literature number SPRU198) describes ways to optimize C and assembly code for the TMS320C6000 DSPs and includes application program examples.

- **TMS320C6000 Assembly Language Tools User's Guide** (literature number SPRU186) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for the 'C6000 generation of devices.

- **TMS320C6000 Optimizing C Compiler User's Guide** (literature number SPRU187) describes the 'C6000 C compiler and the assembly optimizer. This C compiler accepts ANSI standard C source code and produces assembly language source code for the 'C6000 generation of devices. The assembly optimizer helps you optimize your assembly code.

- **TMS320C6x C Source Debugger User's Guide** (literature number SPRU188) tells you how to invoke the 'C6x simulator and emulator versions of the C source debugger interface. This book discusses various aspects of the debugger, including command entry, code execution, data management, breakpoints, profiling, and analysis.

- **TMS320C6201, TMS320C6201B Digital Signal Processors Data Sheet** (literature number SPRS051) describes the features of the TMS320C6201 and TMS320C6201B fixed-point DSPs and provides pinouts, electrical specifications, and timings for the devices.

- **TMS320C6202 Digital Signal Processor Data Sheet** (literature number SPRS072) describes the features of the TMS320C6202 fixed-point DSP and provides pinouts, electrical specifications, and timings for the device.

- **TMS320C6701 Digital Signal Processor Data Sheet** (literature number SPRS067) describes the features of the TMS320C6701 floating-point DSP and provides pinouts, electrical specifications, and timings for the device.

- **TMS320C6211 Digital Signal Processor Data Sheet** (literature number SPRS073) describes the features of the TMS320C6211 fixed-point DSP and provides pinouts, electrical specifications, and timings for the device.

- **TMS320C6711 Digital Signal Processor Data Sheet** (literature number SPRS088) describes the features of the TMS320C6711 fixed-point DSP and provides pinouts, electrical specifications, and timings for the device.

### Trademarks

320 Hotline On-line, VelociTI, and XDS510 are trademarks of Texas Instruments Incorporated.

PC is a trademark of International Business Machines Corporation.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

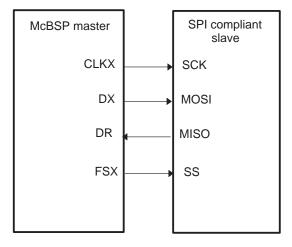

SPI is a trademark of Motorola, Inc.

ST-BUS is a trademark of Mitel.

Windows and Windows NT are registered trademarks of Microsoft Corporation.

### If You Need Assistance . . .

| World-Wide Web Sites                                                                                                                                      |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| TI Online http://www.ti.com                                                                                                                               |                      |

| Semiconductor Product Information Center (PIC) http://www.ti.com/sc/docs/pic/home.htm                                                                     |                      |

| DSP Solutionshttp://www.ti.com/dsps320 Hotline On-line ™http://www.ti.com/sc/docs/dsps/support.htm                                                        |                      |

| · · · ·                                                                                                                                                   |                      |

| North America, South America, Central America                                                                                                             |                      |

| Product Information Center (PIC) (972) 644-5580                                                                                                           |                      |

| TI Literature Response Center U.S.A. (800) 477-8924                                                                                                       |                      |

| Software Registration/Upgrades(214) 638-0333Fax:(214) 638-7742U.S.A. Factory Repair/Hardware Upgrades(281) 274-2285                                       |                      |

| U.S. Technical Training Organization (972) 644-5580                                                                                                       |                      |

| DSP Hotline Email: dsph@ti.com                                                                                                                            |                      |

| DSP Internet BBS via anonymous ftp to ftp://ftp.ti.com/pub/tms320bbs                                                                                      |                      |

| Europe, Middle East, Africa                                                                                                                               |                      |

| European Product Information Center (EPIC) Hotlines:                                                                                                      |                      |

| Multi-Language Support +33 1 30 70 11 69 Fax: +33 1 30 70 10 32                                                                                           |                      |

| Email: epic@ti.com                                                                                                                                        |                      |

| Deutsch +49 8161 80 33 11 or +33 1 30 70 11 68                                                                                                            |                      |

| English +33 1 30 70 11 65                                                                                                                                 |                      |

| Francais +33 1 30 70 11 64                                                                                                                                |                      |

| Italiano +33 1 30 70 11 67                                                                                                                                |                      |

| EPIC Modem BBS +33 1 30 70 11 99                                                                                                                          |                      |

| European Factory Repair+33 4 93 22 25 40Europe Customer Training HelplineFax: +49 81 61 80 40 10                                                          |                      |

|                                                                                                                                                           |                      |

| Asia-Pacific                                                                                                                                              |                      |

| Literature Response Center +852 2 956 7288 Fax: +852 2 956 2200                                                                                           |                      |

| Hong Kong DSP Hotline         +852 2 956 7268         Fax: +852 2 956 1002           Kong DSP Hotling         -22 2 551 2224         Fax: +852 2 956 1002 |                      |

| Korea DSP Hotline         +82 2 551 2804         Fax: +82 2 551 2828           Korea DSP Modern PRS         +82 3 551 2014                                |                      |

| Korea DSP Modem BBS         +82 2 551 2914           Singapore DSP Hotline         Fax: +65 390 7179                                                      |                      |

| Taiwan DSP Hotline +886 2 377 1450 Fax: +886 2 377 2718                                                                                                   |                      |

| Taiwan DSP Modem BBS +886 2 376 2592                                                                                                                      |                      |

| Taiwan DSP Internet BBS via anonymous ftp to ftp://dsp.ee.tit.edu.tw/pub/TI/                                                                              |                      |

| 🗋 Japan                                                                                                                                                   |                      |

| Product Information Center +0120-81-0026 (in Japan) Fax: +0120-81-0036 (in Japan)                                                                         |                      |

| +03-3457-0972 or (INTL) 813-3457-0972 Fax: +03-3457-1259 or (INTL) 813                                                                                    | -3457-1259           |

| DSP Hotline +03-3769-8735 or (INTL) 813-3769-8735 Fax: +03-3457-7071 or (INTL) 813                                                                        |                      |

| DSP BBS via Nifty-Serve Type "Go TIASP"                                                                                                                   |                      |

| Documentation                                                                                                                                             |                      |

| When making suggestions or reporting errors in documentation, please include the following information                                                    | that is on the title |

| page: the full title of the book, the publication date, and the literature number.                                                                        |                      |

| Mail: Texas Instruments Incorporated Email: dsph@ti.com                                                                                                   |                      |

| Technical Documentation Services, MS 702                                                                                                                  |                      |

| P.O. Box 1443                                                                                                                                             |                      |

| Houston, Texas 77251-1443                                                                                                                                 |                      |

Note: When calling a Literature Response Center to order documentation, please specify the literature number of the book.

# Contents

| 1 |            |         | ۱                                                                                                                                           | 1-1 |

|---|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | TMS        | 320C620 | 01 and TMS320C6701 DSPs and lists their key features.                                                                                       |     |

|   | 1.1        | TMS32   | 20 Family Overview                                                                                                                          | 1-2 |

|   |            | 1.1.1   | History of TMS320 DSPs                                                                                                                      | 1-2 |

|   |            | 1.1.2   | Typical Applications for the TMS320 Family                                                                                                  | 1-2 |

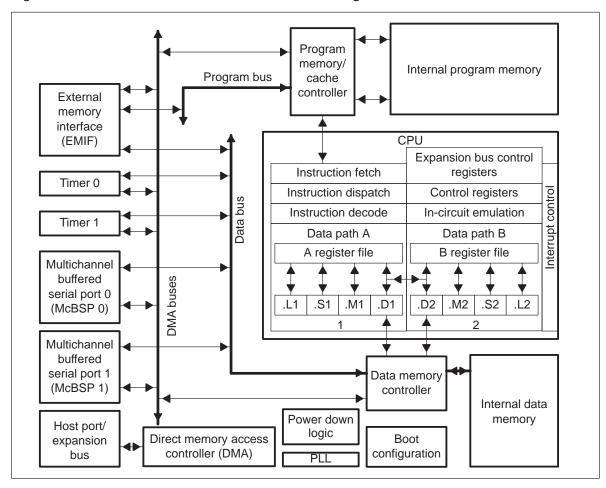

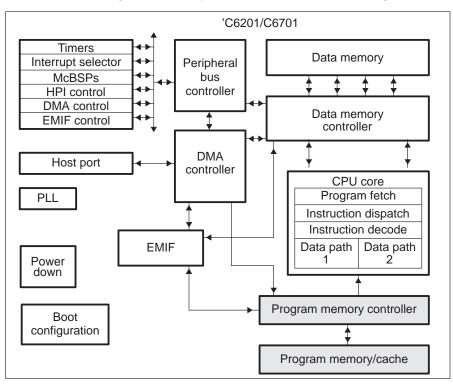

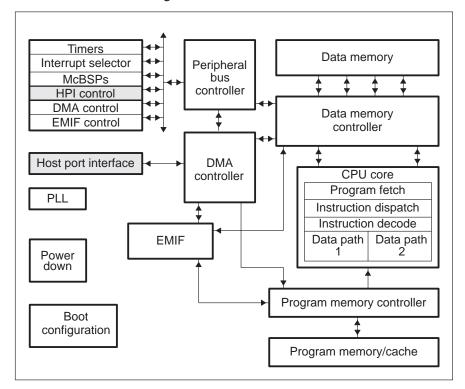

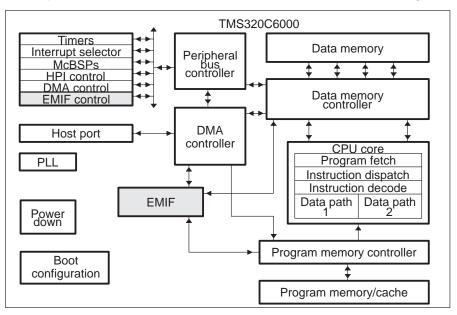

|   | 1.2        | Overvi  | iew of the TMS320C6000 Platform of DSPs                                                                                                     | 1-4 |

|   | 1.3        | Featur  | res and Options of the TMS320C6000 Devices                                                                                                  | 1-5 |

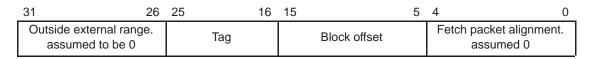

|   | 1.4        | Overvi  | iew of TMS320C6000 Memory                                                                                                                   | 1-6 |

|   | 1.5        | Overvi  | iew of TMS320C6000 Peripherals                                                                                                              | 1-8 |

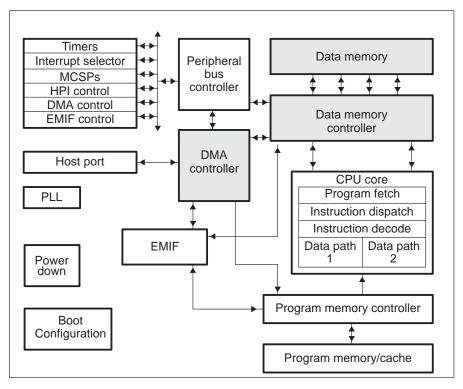

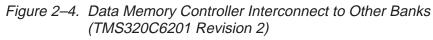

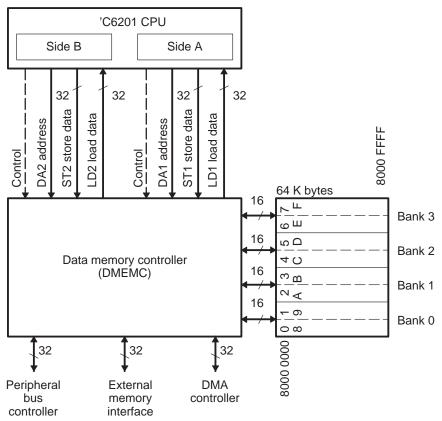

| 2 | TMS        | 320C620 | 01/C6701 Program and Data Memory                                                                                                            | 2-1 |

|   |            |         | e program and data memory system for the TMS320C6201/C6701. This includ<br>nory organization,cache modes, DMA and peripheral bus operation. | les |

|   | , 0        |         |                                                                                                                                             | 0.0 |

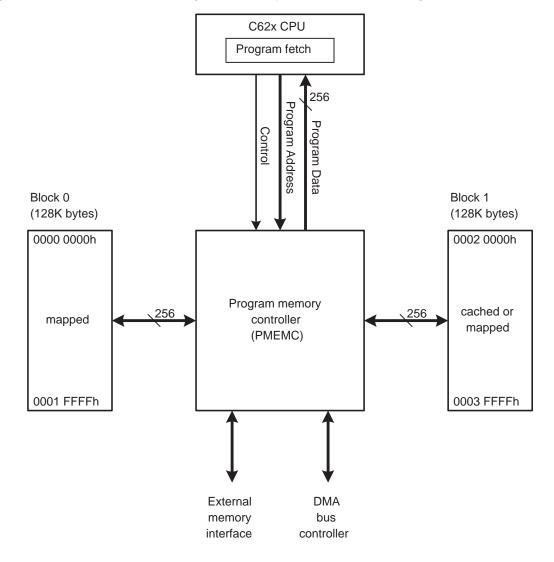

|   | 2.1        | -       | am Memory Controller                                                                                                                        |     |

|   | 2.2        | 2.2.1   | al Program Memory                                                                                                                           |     |

|   |            | 2.2.1   | Internal Program Memory Modes                                                                                                               |     |

|   | 2.3        |         | Cache Architecture                                                                                                                          |     |

|   | 2.3<br>2.4 |         | Controller Access to Program Memory                                                                                                         |     |

|   | 2.4<br>2.5 |         | Memory Access                                                                                                                               |     |

|   | 2.5        |         | al Data Memory Organization                                                                                                                 |     |

|   | 2.0        | 2.6.1   | TMS320C6201 Revision 2                                                                                                                      |     |

|   |            | 2.6.2   | TMS320C6201 Revision 2                                                                                                                      | -   |

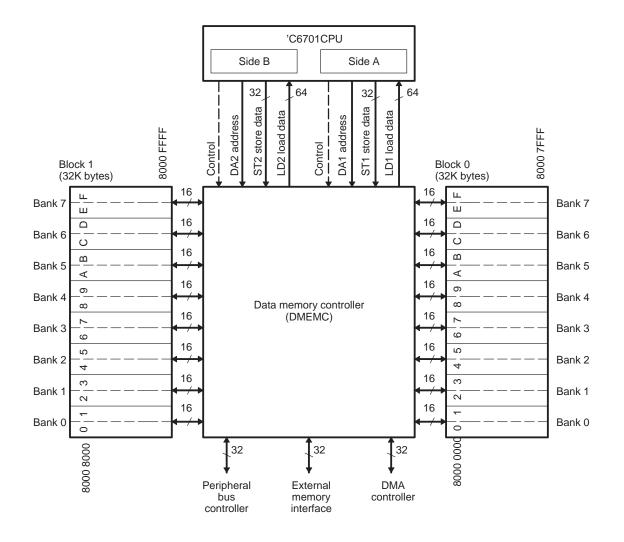

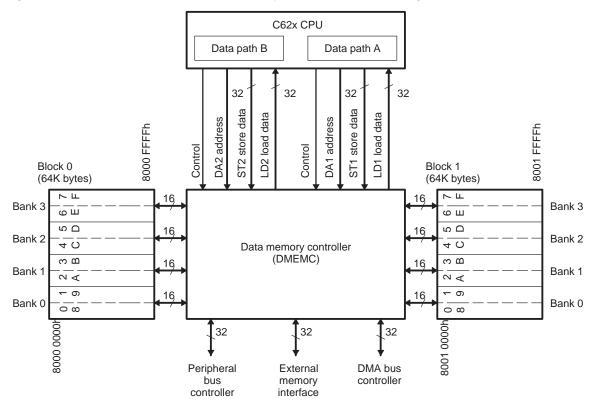

|   |            | 2.6.3   | TMS320C6701                                                                                                                                 |     |

|   |            | 2.6.4   | Data Alignment                                                                                                                              |     |

|   |            | 2.6.5   | Dual CPU Accesses to Internal Memory                                                                                                        |     |

|   |            | 2.6.6   | DMA Accesses to Internal Memory                                                                                                             |     |

|   |            | 2.6.7   | Data Endianness                                                                                                                             |     |

|   | 2.7        | -       | neral Bus                                                                                                                                   |     |

|   | 2.1        | 2.7.1   | Byte and Halfword Access                                                                                                                    |     |

|   |            | 2.7.1   | CPU Wait States                                                                                                                             |     |

|   |            | 2.7.3   | Arbitration Between the CPU and the DMA Controller                                                                                          |     |

|   |            | 2.7.0   |                                                                                                                                             |     |

| 3 | TMS3  | 20C620    | 2 Program and Data Memory                            | 3-1  |

|---|-------|-----------|------------------------------------------------------|------|

|   | Desci | ribes the | 6202 program memory controller.                      |      |

|   | 3.1   | TMS32     | 0C6202 Program Memory Controller                     | 3-2  |

|   | 3.2   |           | y Mapped Operation                                   |      |

|   | 3.3   | Cache     | Operation                                            | 3-5  |

|   | 3.4   | Bootloa   | ad Operation                                         | 3-6  |

|   | 3.5   | TMS32     | OC6202 Data Memory Controller                        | 3-7  |

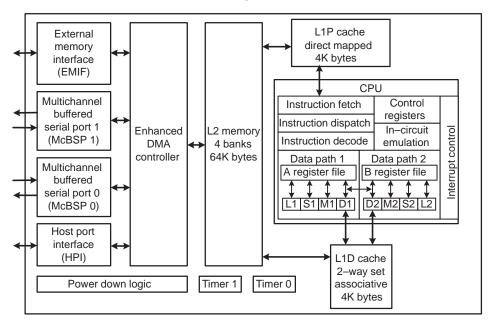

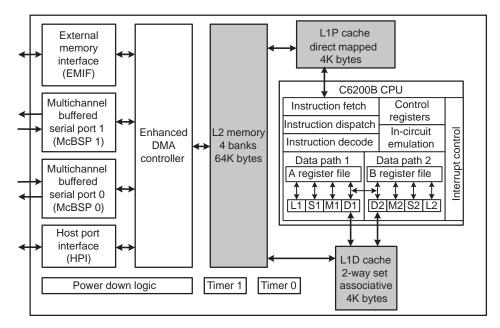

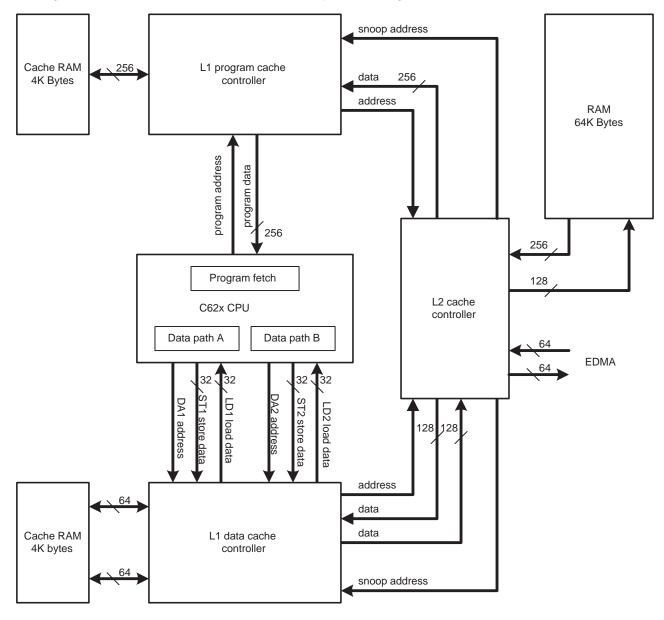

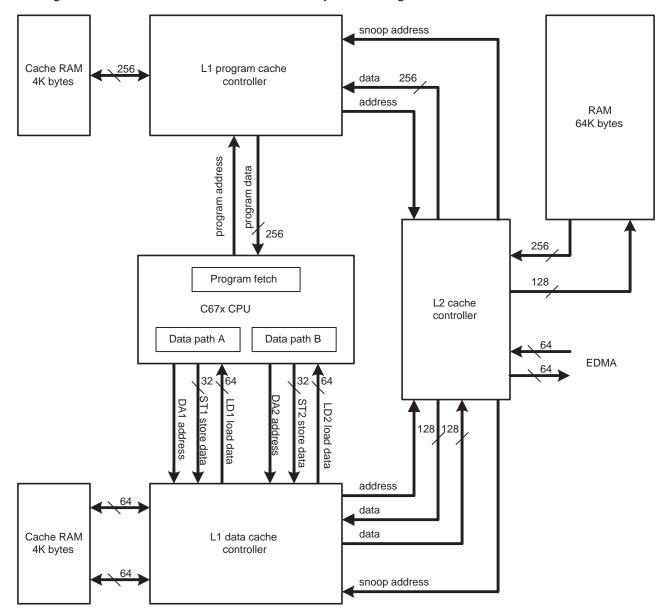

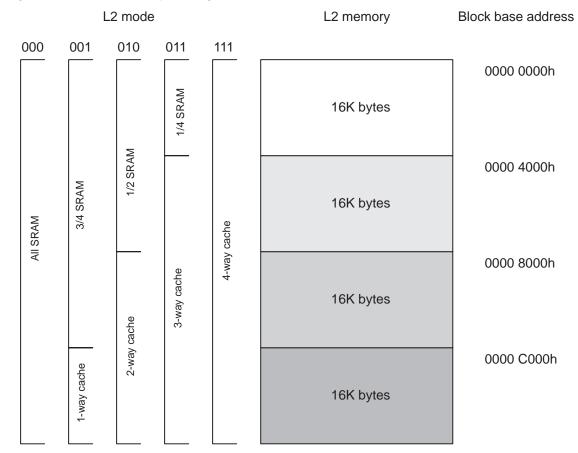

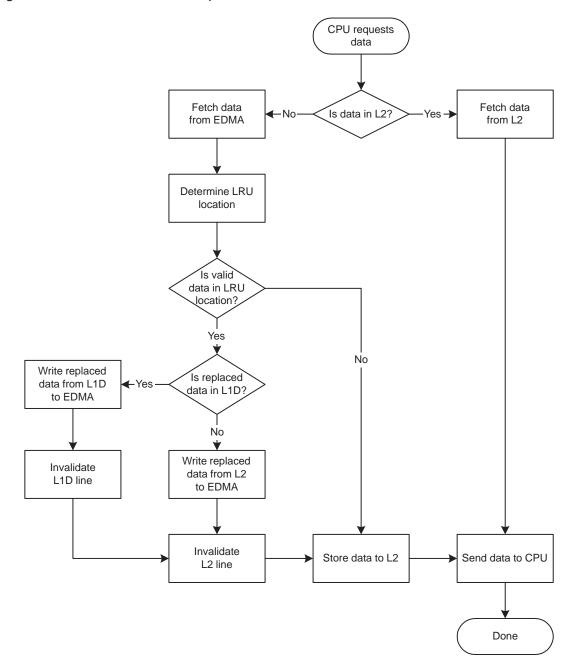

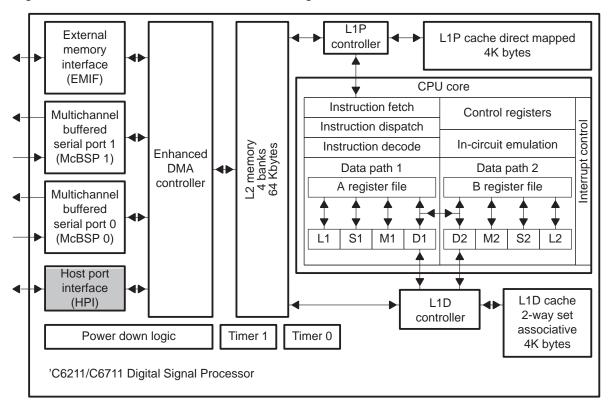

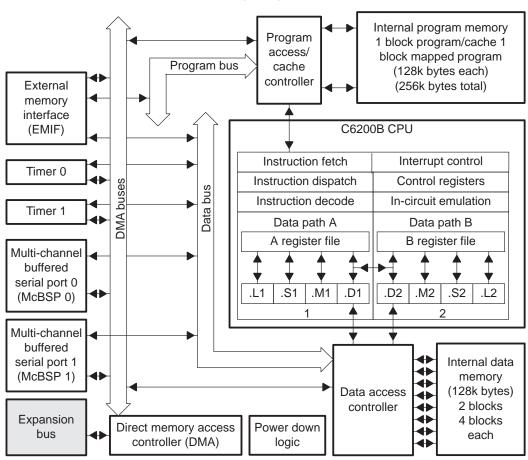

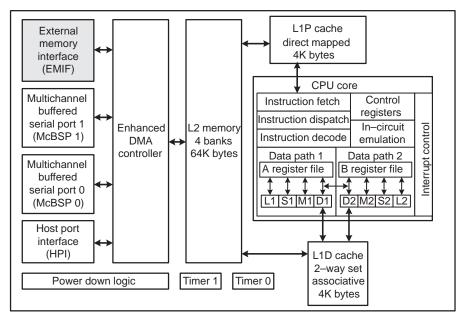

| 4 |       |           | 1/C6711                                              |      |

|   | Two-l | _evel In  | ternal Memory                                        | 4-1  |

|   | Desci | ribes the | program and data memory for the TMS320C6211/C6711.   |      |

|   | 4.1   | Overvie   | ew                                                   | 4-2  |

|   | 4.2   | Interna   | I Memory Control Registers                           | 4-5  |

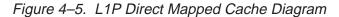

|   | 4.3   | L1P De    | escription                                           | 4-6  |

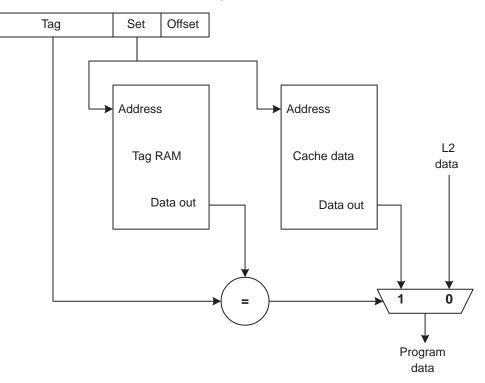

|   | 4.4   |           | escription                                           |      |

|   | 4.5   |           | cription                                             |      |

|   |       | 4.5.1     | L2 Interfaces                                        |      |

|   |       | 4.5.2     | L2 Operation                                         |      |

|   |       | 4.5.3     | L2 EDMA Service                                      |      |

|   |       | 4.5.4     | L2 Invalidation                                      | 1-21 |

| 5 | Direc | t Memo    | ry Access (DMA) Controller                           | 5-1  |

|   | Desci | ribes the | direct memory access controller operation.           |      |

|   | 5.1   | Overvie   | ew                                                   | 5-2  |

|   | 5.2   | DMA R     | egisters                                             | 5-5  |

|   |       | 5.2.1     | DMA Channel Control Registers                        | 5-8  |

|   | 5.3   | Memor     | у Мар                                                | 5-12 |

|   | 5.4   |           | g a Block Transfer                                   | 5-13 |

|   |       | 5.4.1     | DMA Autoinitialization 5                             | 5-13 |

|   | 5.5   | Transfe   | er Counting                                          | 5-16 |

|   | 5.6   | Synchr    | onization: Triggering DMA Transfers 5                | 5-17 |

|   |       | 5.6.1     | Latching of DMA Channel Event Flags 5                |      |

|   |       | 5.6.2     | Automated Event Clearing 5                           |      |

|   |       | 5.6.3     | Synchronization Control 5                            | 5-19 |

|   | 5.7   | Addres    | s Generation 5                                       |      |

|   |       | 5.7.1     | Basic Address Adjustment 5                           |      |

|   |       | 5.7.2     | Address Adjustment With the Global Index Registers 5 |      |

|   |       | 5.7.3     | Element Size, Alignment, and Endianness 5            |      |

|   |       | 5.7.4     | Using a Frame Index to Reload Addresses              |      |

|   |       | 5.7.5     | Transferring a Large Single Block                    |      |

|   |       | 5.7.6     | Sorting                                              |      |

|   | 5.8   | •         | hannel Operation                                     |      |

|   |       | 5.8.1     | Split DMA Operation                                  |      |

|   |       | 5.8.2     | Split Address Generation 5                           | 5-29 |

|   | 5.9  | Resource Arbitration and Priority Configuration                      | 5-30 |

|---|------|----------------------------------------------------------------------|------|

|   |      | 5.9.1 DMA Auxiliary Control Register and Priority Between Channels 5 | 5-30 |

|   |      | 5.9.2 Switching Channels 5                                           | 5-32 |

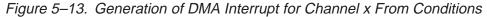

|   | 5.10 | DMA Channel Condition Determination 5                                | 5-33 |

|   |      | 5.10.1 Definition of Channel Conditions 5                            |      |

|   | 5.11 | DMA Controller Structure 5                                           | 5-35 |

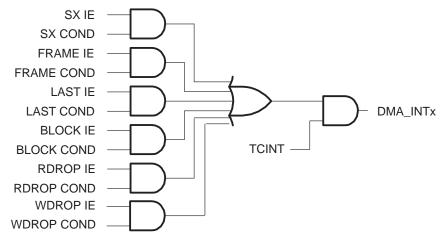

|   |      | 5.11.1 Read and Write Buses 5                                        | 5-35 |

|   |      | 5.11.2 DMA FIFO 5                                                    | 5-36 |

|   |      | 5.11.3 Internal Holding Registers 5                                  | 5-37 |

|   |      | 5.11.4 DMA Performance 5                                             | 5-38 |

|   | 5.12 | DMA Action Complete Pins 5                                           | 5-38 |

|   | 5.13 | Emulation                                                            | 5-38 |

| ~ |      | A Constrallar                                                        | ~ 4  |

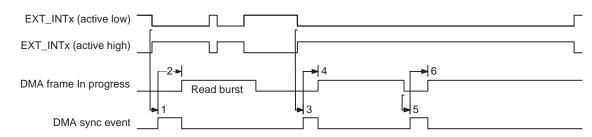

| 6 |      | A Controller                                                         | 6-1  |

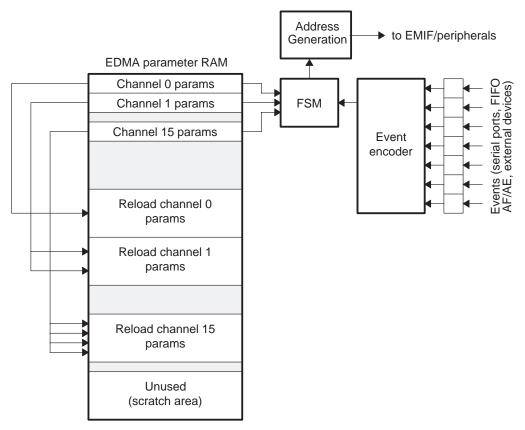

|   |      | chapter describes the new enhanced DMA for the TMS320C6211/6711.     |      |

|   | 6.1  | Overview                                                             |      |

|   | 6.2  | EDMA Terminology                                                     |      |

|   | 6.3  | Event Processing and EDMA Control Registers                          |      |

|   | 6.4  | Event Encoder                                                        |      |

|   | 6.5  | Parameter RAM (PaRAM)                                                |      |

|   |      | 6.5.1 EDMA Transfer Parameter Entry 6                                |      |

|   | 6.6  | EDMA Transfer Parameters 6                                           |      |

|   |      | 6.6.1 Options Parameter 6                                            |      |

|   |      | 6.6.2 SRC/DST Address 6                                              |      |

|   |      | 6.6.3 Element Count                                                  |      |

|   |      | 6.6.4 Frame/Array Count 6                                            |      |

|   |      | 6.6.5 Element/(Frame/Array) Index 6                                  |      |

|   |      | 6.6.6 Element Count Reload                                           |      |

|   |      | 6.6.7 Link Address                                                   |      |

|   | 6.7  | Initiating an EDMA Transfer6                                         |      |

|   |      | 6.7.1 Synchronization of EDMA Transfers                              |      |

|   | 6.8  | Types of EDMA Transfers                                              |      |

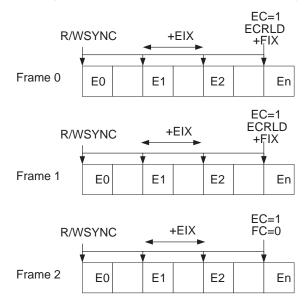

|   |      | 6.8.1 Non-2Dimensional Transfers 6                                   |      |

|   |      | 6.8.2 2-Dimensional Transfers 6                                      |      |

|   | 6.9  | Linking EDMA Transfers                                               |      |

|   | 6.10 | 5                                                                    |      |

|   | 6.11 | Element and Frame/Array Count Updates 6                              |      |

|   |      | 6.11.1 Element Count Reload (ECRLD) 6                                | 5-28 |

|   | 6.12 | Src/Dst Address Updates 6                                            |      |

|   | 6.13 | EDMA Interrupt Generation                                            |      |

|   |      | 6.13.1 EDMA Interrupt Servicing by the CPU                           |      |

|   |      | 6.13.2 Chaining EDMA Channels by an Event                            |      |

|   | 6.14 | Resource Arbitration and Priority Processing                         |      |

|   | 6.15 | EDMA Performance                                                     | 6-37 |

|   |      |                                                                      |      |

|   | 6.16  | Quick [   | DMA (QDMA)                                                                  | 38  |

|---|-------|-----------|-----------------------------------------------------------------------------|-----|

|   |       |           | QDMA Registers                                                              |     |

|   |       |           | QDMA Register Access                                                        |     |

|   |       |           | Pseudo Mappings                                                             |     |

|   |       |           | QDMA Performance                                                            |     |

|   |       |           | QDMA Stalls and Priority                                                    |     |

|   |       | 011010    |                                                                             | ••• |

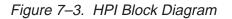

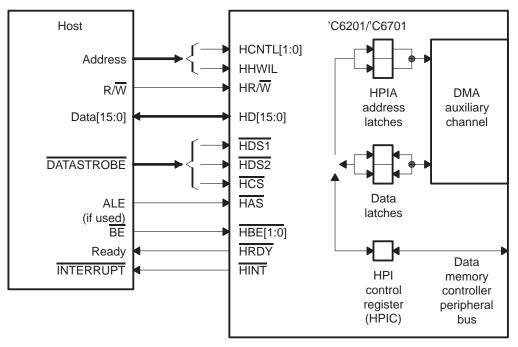

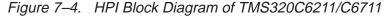

| 7 | Host- | Port Int  | erface                                                                      | -1  |

|   | Desci | ribes the | host-port interface (HPI) used to access 'C6201 and 'C6701 memory-map space |     |

|   | by ex | ternal pr | ocessors.                                                                   |     |

|   | 7.1   | Overvie   | ew                                                                          | -2  |

|   | 7.2   |           | gnal Descriptions                                                           |     |

|   |       | 7.2.1     | Data Bus: HD[15:0]                                                          |     |

|   |       | 7.2.2     | Access Control Select: HCNTL[1:0]                                           |     |

|   |       | 7.2.3     | Halfword Identification Select: HHWIL                                       |     |

|   |       | 7.2.4     | Byte Enables: HBE[1:0]                                                      |     |

|   |       | 7.2.5     | Read/Write Select: HR/W                                                     |     |

|   |       | 7.2.6     | Ready: HRDY                                                                 |     |

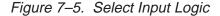

|   |       | 7.2.7     | Strobes: HCS, HDS1, HDS2                                                    |     |

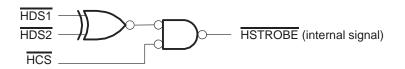

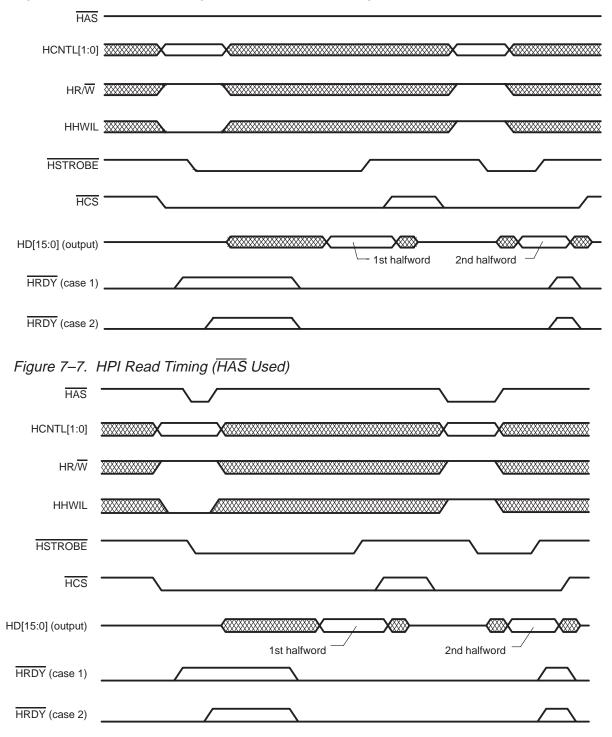

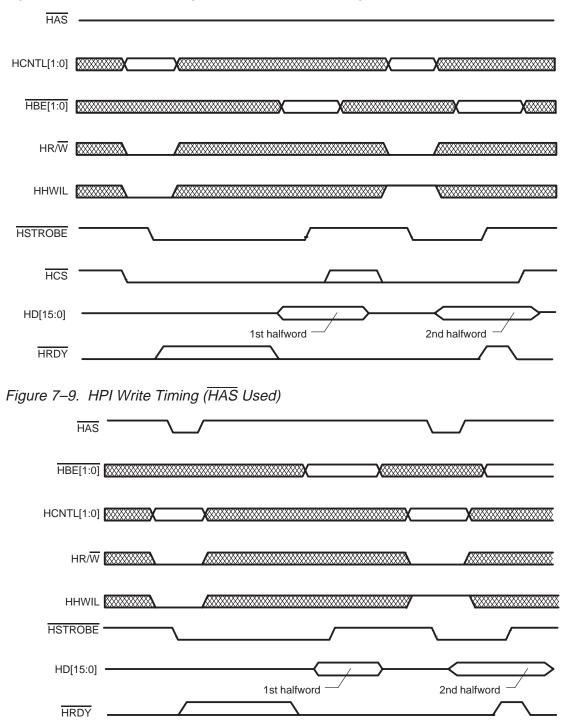

|   |       | 7.2.8     | Address Strobe Input: HAS                                                   |     |

|   |       | 7.2.9     | Interrupt to Host: HINT                                                     |     |

|   |       | 7.2.10    | HPI Bus Access                                                              |     |

|   | 7.3   | HPI Re    | gisters                                                                     | 16  |

|   |       | 7.3.1     | HPI Control Register (HPIC)                                                 |     |

|   |       | 7.3.2     | Software Handshaking Using HRDY and FETCH                                   |     |

|   |       | 7.3.3     | Host Device Using DSPINT to Interrupt the CPU                               |     |

|   |       | 7.3.4     | CPU Using HINT to Interrupt the Host                                        |     |

|   | 7.4   | Host A    | ccess Sequences                                                             |     |

|   |       | 7.4.1     | Host Initialization of HPIC and HPIA                                        | 19  |

|   |       | 7.4.2     | HPID Read Access Without Autoincrement                                      | 20  |

|   |       | 7.4.3     | HPID Read Access With Autoincrement                                         | 22  |

|   |       | 7.4.4     | Host Data Write Access Without Autoincrement                                | 23  |

|   |       | 7.4.5     | HPID Write Access With Autoincrement                                        | 25  |

|   |       | 7.4.6     | Single Halfword Cycles                                                      |     |

|   | 7.5   | Memor     | y Access Through the HPI During Reset 7-2                                   |     |

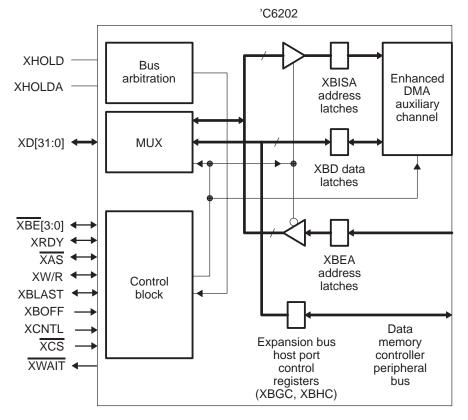

| 8 | Expa  | nsion B   | us                                                                          | -1  |

| - | -     |           | expansion bus used by CPU to access off-chip peripherals, FIFOs and PCI     |     |

|   |       | ace chips |                                                                             |     |

|   | 8.1   | Overvie   | ew                                                                          | -2  |

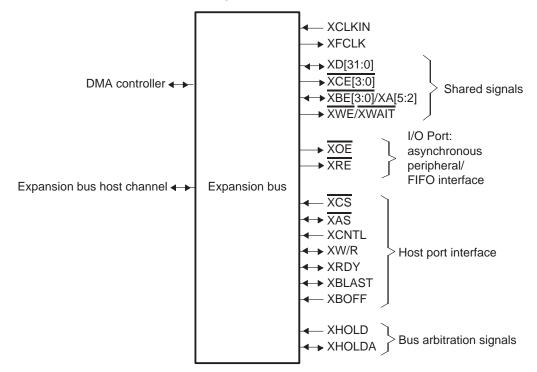

|   | 8.2   | Expans    | sion Bus Signals                                                            | -5  |

|   | 8.3   |           | sion Bus Registers                                                          |     |

|   |       | 8.3.1     | Expansion Bus Host Port Registers 8                                         |     |

|   |       | 8.3.2     | Expansion Bus Global Control Register 8                                     |     |

|   |       | 0.3.2     |                                                                             | -0  |

|   |            | 8.3.3   | XCE Space Control Registers 8-9                                               |

|---|------------|---------|-------------------------------------------------------------------------------|

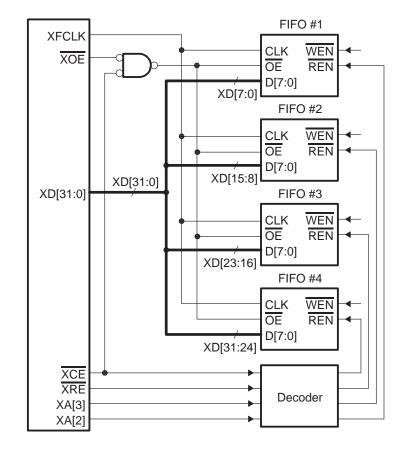

|   | 8.4        | Expans  | sion Bus I/O Port Operation 8-10                                              |

|   |            | 8.4.1   | Asynchronous Mode 8-12                                                        |

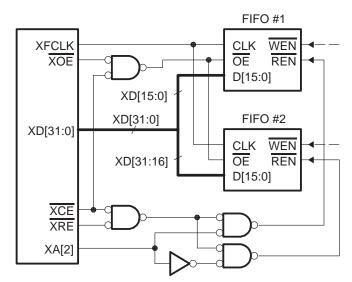

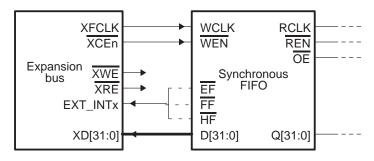

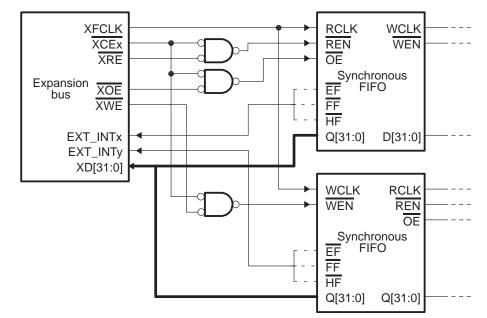

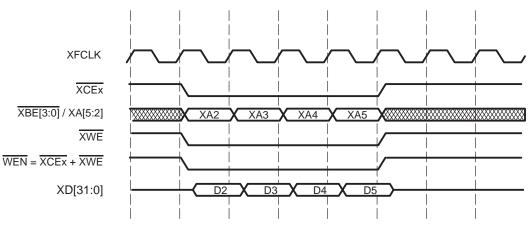

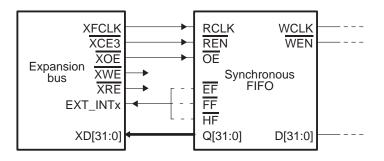

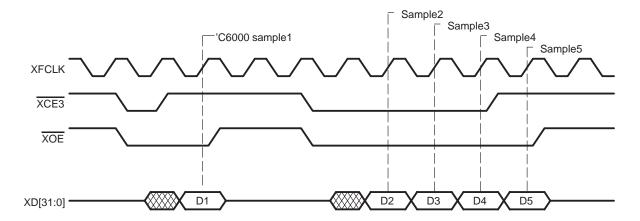

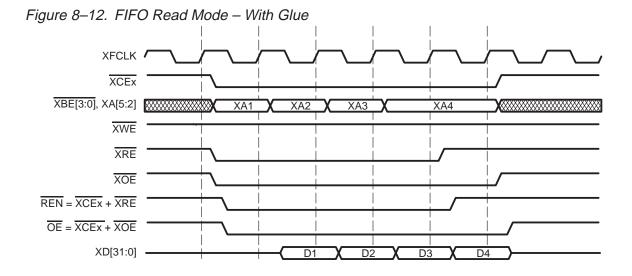

|   |            | 8.4.2   | Synch FIFO Modes 8-13                                                         |

|   |            | 8.4.3   | DMA Transfer Examples 8-20                                                    |

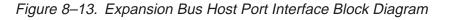

|   | 8.5        | Expans  | sion Bus Host Port Operation 8-22                                             |

|   |            | 8.5.1   | Expansion Bus Host Port Registers Description 8-23                            |

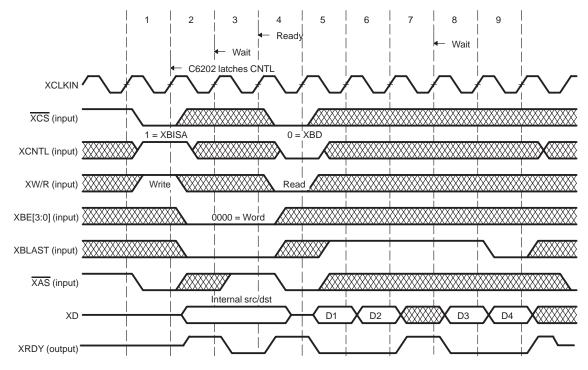

|   |            | 8.5.2   | Synchronous Host Port Mode 8-26                                               |

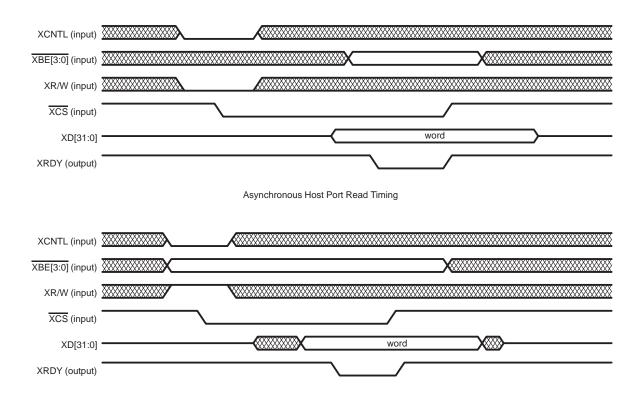

|   |            | 8.5.3   | Asynchronous Host Port Mode 8-41                                              |

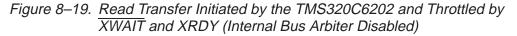

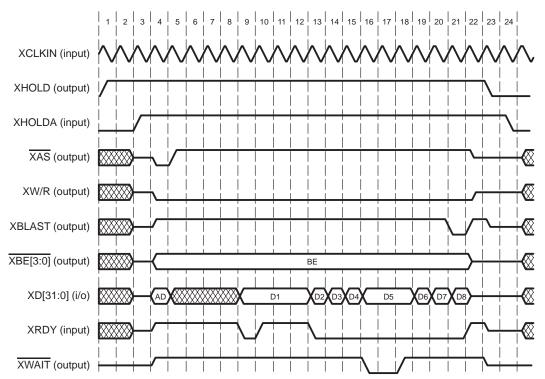

|   | 8.6        | Expans  | sion Bus Arbitration                                                          |

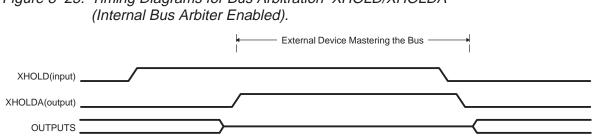

|   |            | 8.6.1   | Internal Bus Arbiter Enabled 8-44                                             |

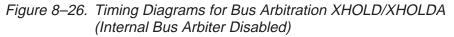

|   |            | 8.6.2   | Internal Bus Arbiter Disabled 8-45                                            |

|   |            | 8.6.3   | Expansion Bus Requestor Priority 8-48                                         |

|   | 8.7        | Boot C  | onfiguration Control via Expansion Bus 8-49                                   |

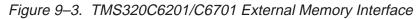

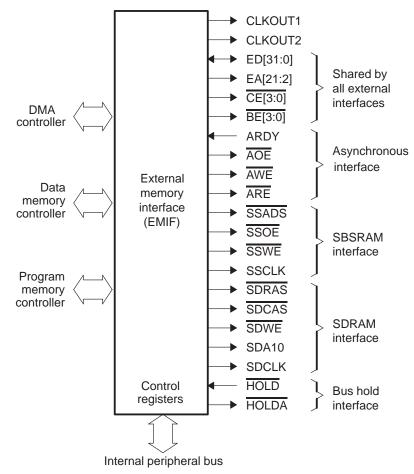

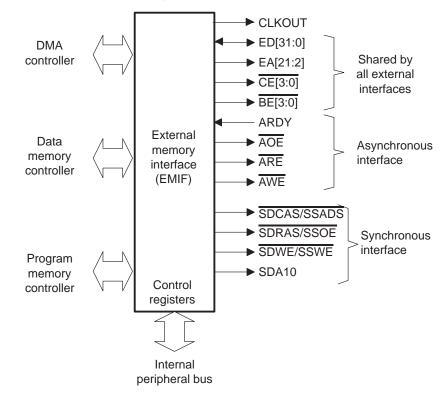

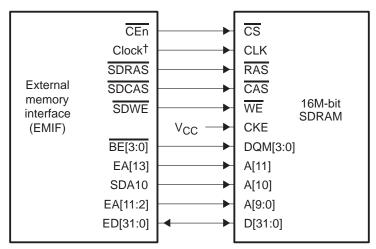

| 9 | Fyter      | nal Men | nory Interface                                                                |

| Ŭ |            |         | external memory interface (EMIF) that the CPU uses to access off-chip memory. |

|   | 9.1        |         | ew                                                                            |

|   | 9.2        |         | ng the EMIF                                                                   |

|   | 9.2<br>9.3 |         | Registers                                                                     |

|   | 0.0        | 9.3.1   | Global Control Register                                                       |

|   |            | 9.3.2   | EMIF CE Space Control Registers                                               |

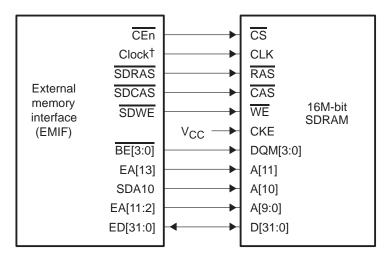

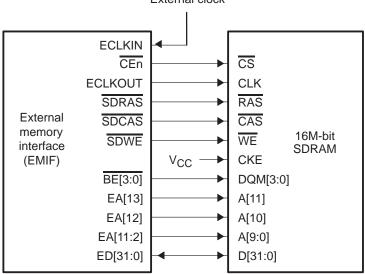

|   |            | 9.3.3   | EMIF SDRAM Control Register                                                   |

|   |            | 9.3.4   | EMIF SDRAM Timing Register                                                    |

|   |            | 9.3.5   | TMS320C6211/C6711 SDRAM Extension Register                                    |

|   | 9.4        |         | VI Interface         9-20                                                     |

|   | 0          | 9.4.1   | SDRAM Initialization                                                          |

|   |            | 9.4.2   | Monitoring Page Boundaries                                                    |

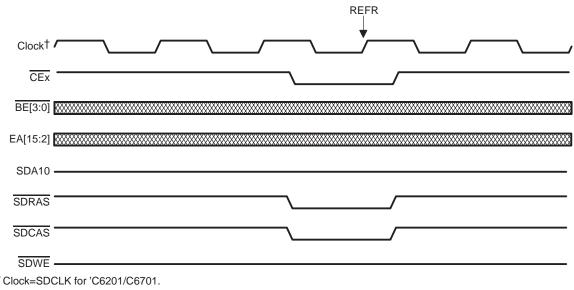

|   |            | 9.4.3   | SDRAM Refresh                                                                 |

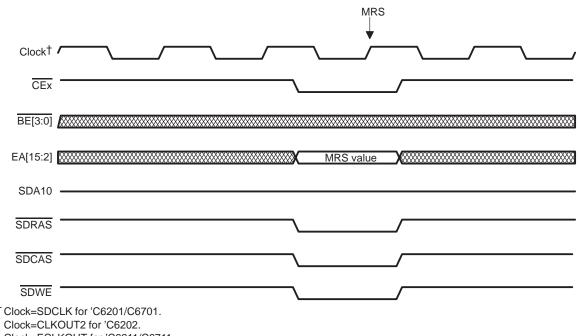

|   |            | 9.4.4   | Mode Register Set                                                             |

|   |            | 9.4.5   | Address Shift                                                                 |

|   |            | 9.4.6   | Timing Requirements                                                           |

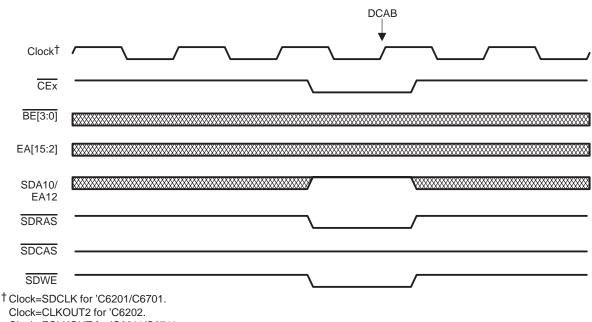

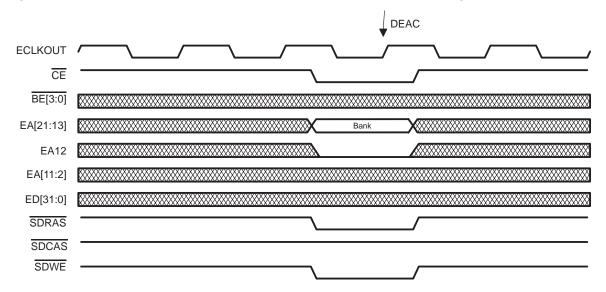

|   |            | 9.4.7   | SDRAM Deactivation                                                            |

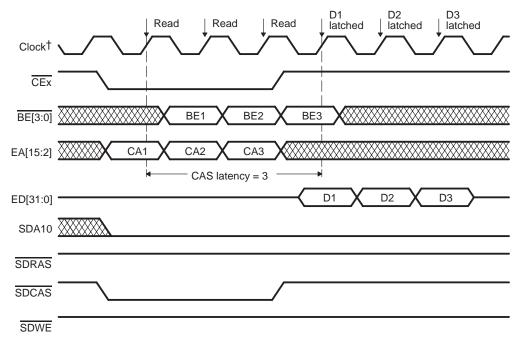

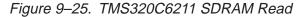

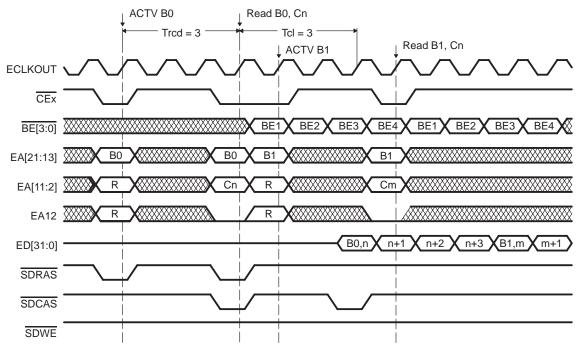

|   |            | 9.4.8   | SDRAM Read                                                                    |

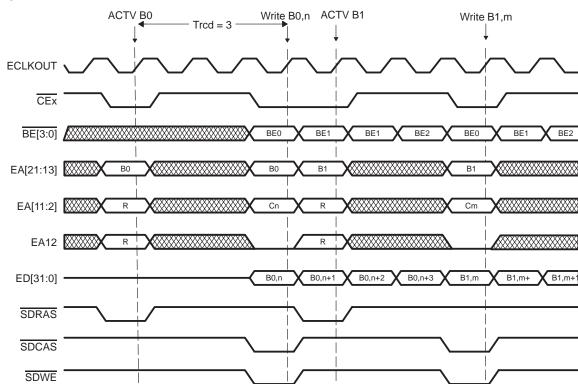

|   |            | 9.4.9   | SDRAM Write                                                                   |

|   |            | 9.4.10  | TMS320C6211/C6711 Seamless Data Access                                        |

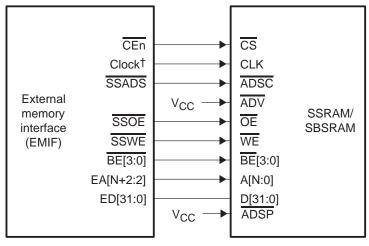

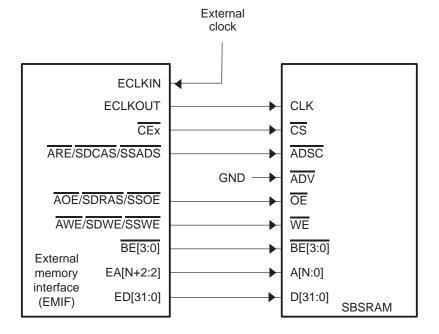

|   | 9.5        | SBSRA   | AM Interface                                                                  |

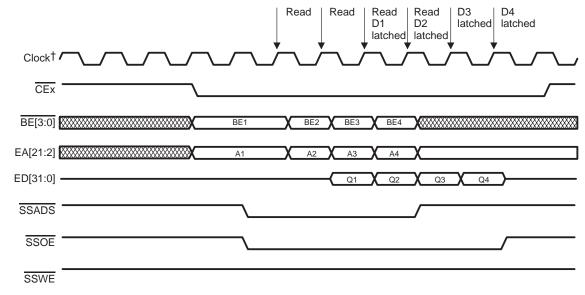

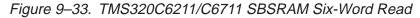

|   |            | 9.5.1   | SBSRAM Reads                                                                  |

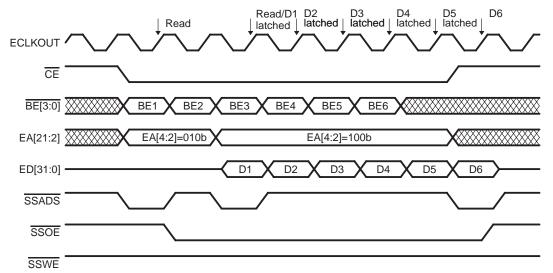

|   |            | 9.5.2   | SBSRAM Writes                                                                 |

|   | 9.6        | Asynch  | nronous Interface                                                             |

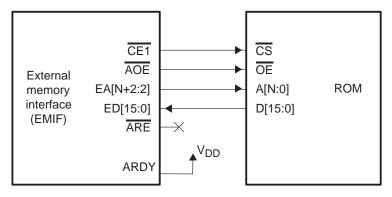

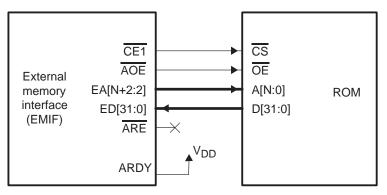

|   |            | 9.6.1   | TMS320C6201/C6202/C6701 ROM Modes                                             |

|   |            | 9.6.2   | Programmable ASRAM Parameters 9-53                                            |

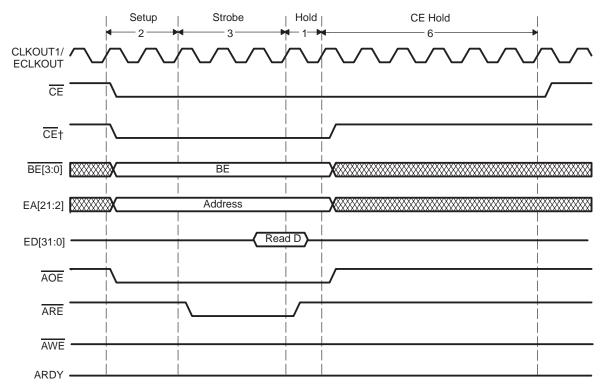

|   |            | 9.6.3   | Asynchronous Reads 9-54                                                       |

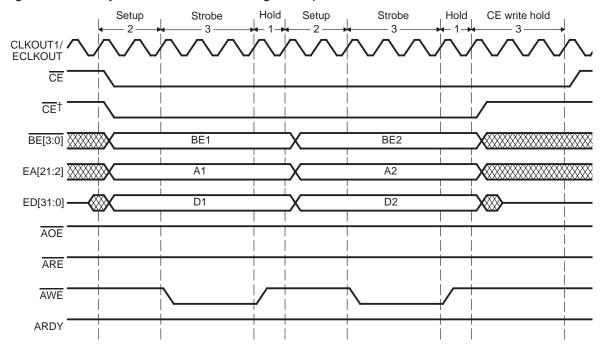

|   |            | 9.6.4   | Asynchronous Writes                                                           |

|   |            |         |                                                                               |

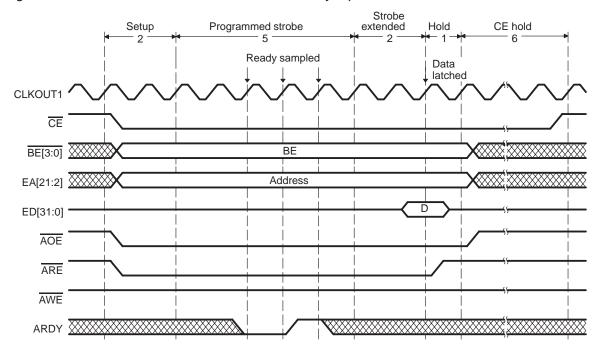

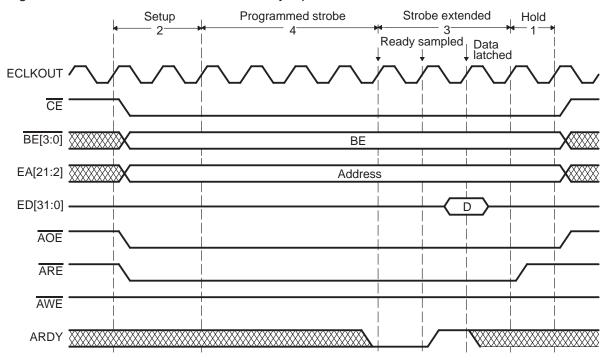

|    | 9.7<br>9.8                    |                                                                                                                                                                                                                                              | Ready Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9-60<br>9-61<br>9-61                                                                                                                      |

|----|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|    | 9.9<br>9.10<br>9.11           | Clock C                                                                                                                                                                                                                                      | ary Conditions When Writing to EMIF Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9-64                                                                                                                                      |

|    | 9.12                          |                                                                                                                                                                                                                                              | Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                           |

| 10 |                               |                                                                                                                                                                                                                                              | and Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10-1                                                                                                                                      |

|    | Desci                         |                                                                                                                                                                                                                                              | boot modes and associated memory maps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                           |

|    | 10.1                          |                                                                                                                                                                                                                                              | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                           |

|    | 10.2                          |                                                                                                                                                                                                                                              | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                           |

|    | 10.3                          |                                                                                                                                                                                                                                              | onfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                           |

|    |                               | 10.3.1                                                                                                                                                                                                                                       | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                           |

|    |                               | 10.3.2                                                                                                                                                                                                                                       | Memory at Reset Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                           |

|    | 10.4                          |                                                                                                                                                                                                                                              | Boot Processes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                           |

|    | 10.4                          |                                                                                                                                                                                                                                              | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                           |

|    |                               | 10.4.1                                                                                                                                                                                                                                       | Input Clock Mode<br>Endian Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                           |

|    |                               |                                                                                                                                                                                                                                              | TMS320C6202 Expansion Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                           |

|    |                               | 10.4.0                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10 10                                                                                                                                     |

|    |                               |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                           |

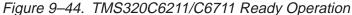

| 11 |                               |                                                                                                                                                                                                                                              | Buffered Serial Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11-1                                                                                                                                      |

| 11 |                               | ribes the                                                                                                                                                                                                                                    | features and operation of the two multichannel buffered serial ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                           |

| 11 | <i>Desci</i><br>11.1          | <i>ribes the</i><br>Feature                                                                                                                                                                                                                  | e features and operation of the two multichannel buffered serial ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11-2                                                                                                                                      |

| 11 | Desci                         | <i>ribes the</i><br>Feature                                                                                                                                                                                                                  | e features and operation of the two multichannel buffered serial ports.<br>es<br>P Interface Signals and Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11-2<br>11-3                                                                                                                              |

| 11 | <i>Desci</i><br>11.1          | ribes the<br>Feature<br>McBSF<br>11.2.1                                                                                                                                                                                                      | e features and operation of the two multichannel buffered serial ports.         es         P Interface Signals and Registers         Serial Port Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11-2<br>11-3<br>11-7                                                                                                                      |

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2                                                                                                                                                                                            | e features and operation of the two multichannel buffered serial ports.<br>es<br>P Interface Signals and Registers<br>Serial Port Configuration<br>Receive and Transmit Control Registers: RCR and XCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11-2<br>11-3<br>11-7<br>11-14                                                                                                             |

| 11 | <i>Desci</i><br>11.1          | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Ti                                                                                                                                                                                 | a features and operation of the two multichannel buffered serial ports.         es         P Interface Signals and Registers         Serial Port Configuration         Receive and Transmit Control Registers: RCR and XCR         ransmission and Reception                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11-2<br>11-3<br>11-7<br>11-14<br>11-18                                                                                                    |

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1                                                                                                                                                                       | e features and operation of the two multichannel buffered serial ports.<br>P Interface Signals and Registers<br>Serial Port Configuration<br>Receive and Transmit Control Registers: RCR and XCR<br>ransmission and Reception<br>Resetting the Serial Port: (R/X)RST, GRST, and RESET                                                                                                                                                                                                                                                                                                                                                                                                                | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18                                                                                           |

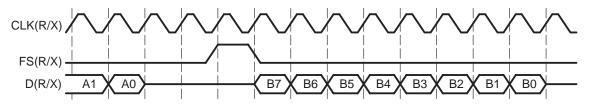

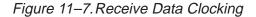

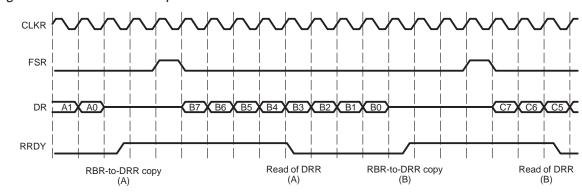

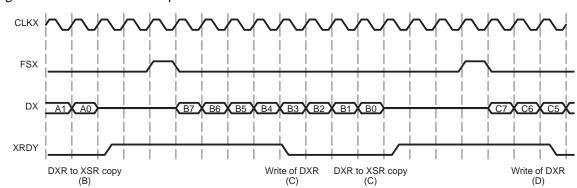

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2                                                                                                                                                             | features and operation of the two multichannel buffered serial ports.     Serial Port Configuration     Receive and Transmit Control Registers: RCR and XCR     Resetting the Serial Port: (R/X)RST, GRST, and RESET     Determining Ready Status                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21                                                                                  |

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2<br>11.3.3                                                                                                                                                   | a features and operation of the two multichannel buffered serial ports.         es         P Interface Signals and Registers         Serial Port Configuration         Receive and Transmit Control Registers: RCR and XCR         ransmission and Reception         Resetting the Serial Port: (R/X)RST, GRST, and RESET         Determining Ready Status         CPU Interrupts: (R/X)INT                                                                                                                                                                                                                                                                                                          | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21<br>11-22                                                                         |

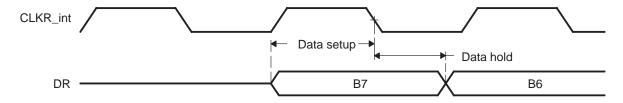

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4                                                                                                                                         | a features and operation of the two multichannel buffered serial ports.         es         P Interface Signals and Registers         Serial Port Configuration         Receive and Transmit Control Registers: RCR and XCR         ransmission and Reception         Resetting the Serial Port: (R/X)RST, GRST, and RESET         Determining Ready Status         CPU Interrupts: (R/X)INT         Frame and Clock Configuration                                                                                                                                                                                                                                                                    | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21<br>11-22<br>11-23                                                                |

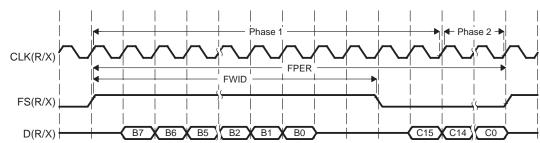

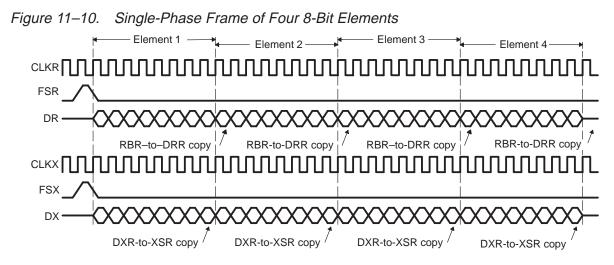

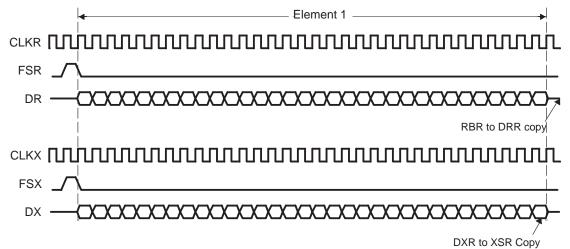

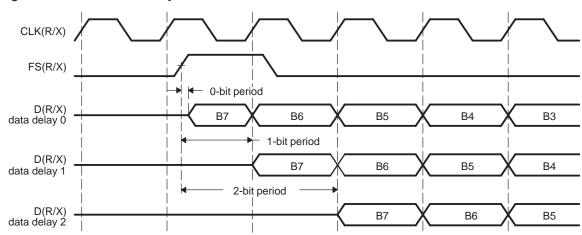

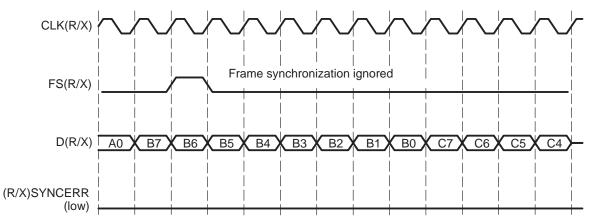

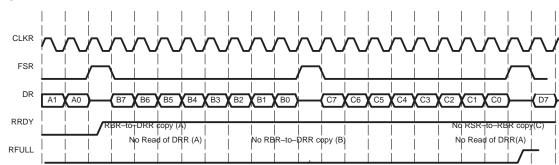

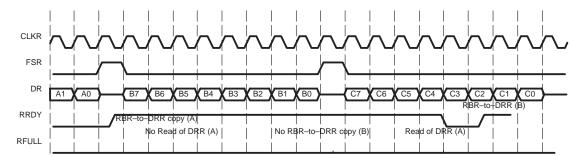

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.3.5                                                                                                                               | features and operation of the two multichannel buffered serial ports.     Serial Port Configuration     Receive and Transmit Control Registers: RCR and XCR     ransmission and Reception     Resetting the Serial Port: (R/X)RST, GRST, and RESET     Determining Ready Status     CPU Interrupts: (R/X)INT     Frame and Clock Configuration     McBSP Standard Operation                                                                                                                                                                                                                                                                                                                          | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21<br>11-22<br>11-23<br>11-33                                                       |

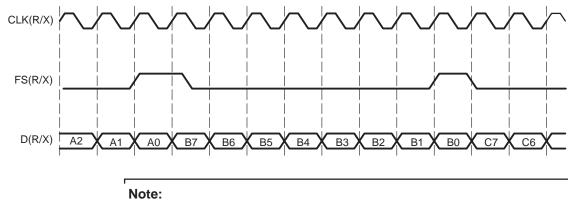

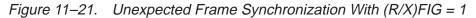

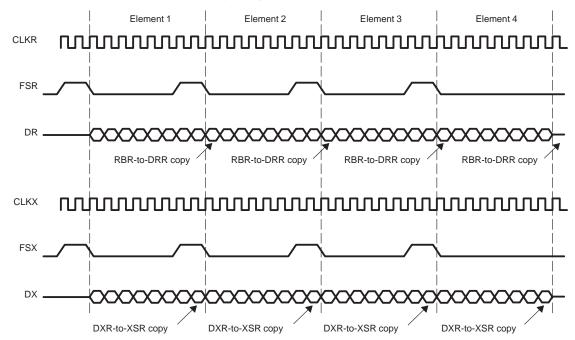

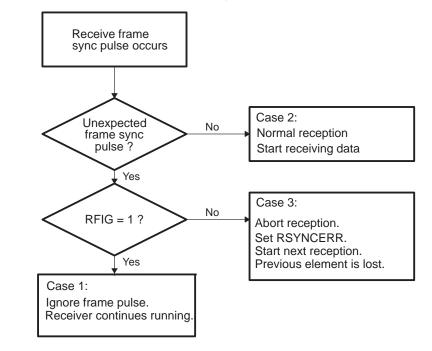

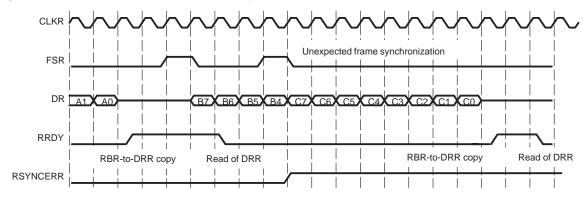

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.3.5<br>11.3.6                                                                                                                     | features and operation of the two multichannel buffered serial ports.     P Interface Signals and Registers     Serial Port Configuration     Receive and Transmit Control Registers: RCR and XCR     ransmission and Reception     Resetting the Serial Port: (R/X)RST, GRST, and RESET     Determining Ready Status     CPU Interrupts: (R/X)INT     Frame and Clock Configuration     McBSP Standard Operation     Frame Synchronization Ignore                                                                                                                                                                                                                                                   | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21<br>11-22<br>11-23<br>11-33<br>11-36                                              |

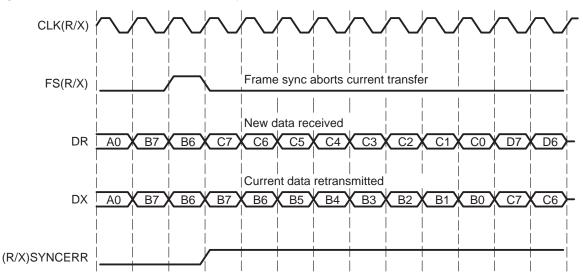

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.3.5<br>11.3.6<br>11.3.7                                                                                                           | features and operation of the two multichannel buffered serial ports.     Serial Port Configuration     Receive and Transmit Control Registers: RCR and XCR     ransmission and Reception     Resetting the Serial Port: (R/X)RST, GRST, and RESET     Determining Ready Status     CPU Interrupts: (R/X)INT     Frame and Clock Configuration     McBSP Standard Operation     Frame Synchronization Ignore     Serial Port Exception Conditions                                                                                                                                                                                                                                                    | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21<br>11-22<br>11-23<br>11-33<br>11-36<br>11-41                                     |

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.3.5<br>11.3.6<br>11.3.7<br>11.3.8                                                                                                 | a features and operation of the two multichannel buffered serial ports.         es         P Interface Signals and Registers         Serial Port Configuration         Receive and Transmit Control Registers: RCR and XCR         ransmission and Reception         Resetting the Serial Port: (R/X)RST, GRST, and RESET         Determining Ready Status         CPU Interrupts: (R/X)INT         Frame and Clock Configuration         McBSP Standard Operation         Frame Synchronization Ignore         Serial Port Exception Conditions         Receive Data Justification and Sign Extension: RJUST                                                                                        | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-21<br>11-22<br>11-23<br>11-33<br>11-36<br>11-41<br>11-49                                     |

| 11 | Descr<br>11.1<br>11.2<br>11.3 | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.3.5<br>11.3.6<br>11.3.7<br>11.3.8<br>11.3.9                                                                                       | a features and operation of the two multichannel buffered serial ports.         es         P Interface Signals and Registers         Serial Port Configuration         Receive and Transmit Control Registers: RCR and XCR         ransmission and Reception         Resetting the Serial Port: (R/X)RST, GRST, and RESET         Determining Ready Status         CPU Interrupts: (R/X)INT         Frame and Clock Configuration         McBSP Standard Operation         Frame Synchronization Ignore         Serial Port Exception Conditions         Receive Data Justification and Sign Extension: RJUST         32-Bit Bit Reversal: (R/X)WDREVRS                                              | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21<br>11-22<br>11-23<br>11-33<br>11-36<br>11-41<br>11-49<br>11-49<br>11-49          |

| 11 | <i>Desci</i><br>11.1<br>11.2  | ribes the<br>Feature<br>McBSF<br>11.2.1<br>11.2.2<br>Data Tr<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.3.5<br>11.3.6<br>11.3.7<br>11.3.8<br>11.3.9<br>μ-LAW                                                                              | a features and operation of the two multichannel buffered serial ports.         es         P Interface Signals and Registers         Serial Port Configuration         Receive and Transmit Control Registers: RCR and XCR         ransmission and Reception         Resetting the Serial Port: (R/X)RST, GRST, and RESET         Determining Ready Status         CPU Interrupts: (R/X)INT         Frame and Clock Configuration         McBSP Standard Operation         Frame Synchronization Ignore         Serial Port Exception Conditions         Receive Data Justification and Sign Extension: RJUST         32-Bit Bit Reversal: (R/X)WDREVRS         /A-LAW Companding Hardware Operation | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21<br>11-22<br>11-23<br>11-33<br>11-33<br>11-36<br>11-49<br>11-49<br>11-50          |

| 11 | Descr<br>11.1<br>11.2<br>11.3 | $\begin{array}{c} \text{ibes the} \\ \text{Feature} \\ \text{McBSF} \\ 11.2.1 \\ 11.2.2 \\ \text{Data Tr} \\ 11.3.1 \\ 11.3.2 \\ 11.3.3 \\ 11.3.4 \\ 11.3.5 \\ 11.3.6 \\ 11.3.7 \\ 11.3.8 \\ 11.3.9 \\ \mu\text{-LAW} \\ 11.4.1 \end{array}$ | a features and operation of the two multichannel buffered serial ports.         es         P Interface Signals and Registers         Serial Port Configuration         Receive and Transmit Control Registers: RCR and XCR         ransmission and Reception         Resetting the Serial Port: (R/X)RST, GRST, and RESET         Determining Ready Status         CPU Interrupts: (R/X)INT         Frame and Clock Configuration         McBSP Standard Operation         Frame Synchronization Ignore         Serial Port Exception Conditions         Receive Data Justification and Sign Extension: RJUST         32-Bit Bit Reversal: (R/X)WDREVRS         /A-LAW Companding Hardware Operation | 11-2<br>11-3<br>11-7<br>11-14<br>11-18<br>11-18<br>11-21<br>11-22<br>11-23<br>11-33<br>11-36<br>11-49<br>11-49<br>11-50<br>11-51          |