| Name      | CM                          | Due date: Thursday, 25 Sept. 2003 |  |  |

|-----------|-----------------------------|-----------------------------------|--|--|

| ECE130-03 | Homework #7                 | Fall 2003                         |  |  |

| 1         | (Combinational Circuit Desi | an)                               |  |  |

Fill the following truth table for a two-bit adder that will generate a two-bit sum  $S_1$   $S_0$  and one-bit carry C from  $A_1$   $A_0$  +  $B_1$   $B_0$ , where  $A_1$   $A_0$  and  $B_1$   $B_0$  are two bit unsigned numbers.

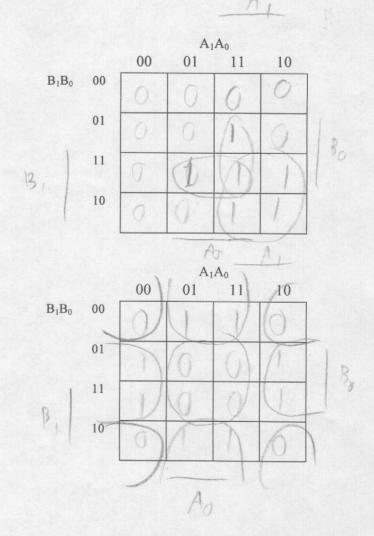

Obtain a minimized sum-of-products expression for C and a minimized product-of-sums expression for S<sub>0</sub>.

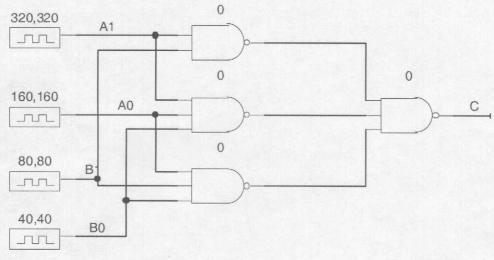

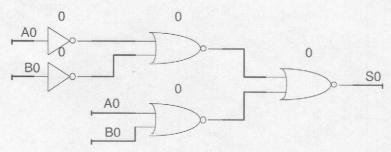

Build an NAND-NAND circuit for C and an NOR-BOR circuit for  $S_0$  with gates from Simulation.Gate.clf library on LogicWorks 4. Set all gate delays to be zero and simulate the circuits to find all possible output combinations. Tie the unused gate inputs to proper logic values.

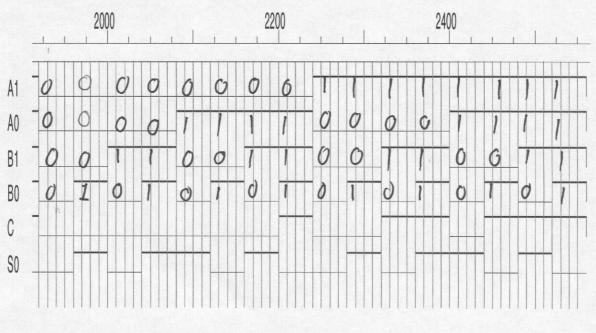

Attach the circuit schematic with all delays visible and one segment of the six waveforms showing all input combinations. Mark the truth table on the waveforms.

$$\mathbf{C} = A_1 B_1 + A_2 A_0 B_0 + A_0 B_1 B_0$$

$$\mathbf{S}_0 = (\overline{A}_0 + \overline{B}_0)(A_0 + \overline{B}_0)$$

| $A_1$ | $A_0$ | $B_1$ | $B_0$ | C   | $S_1$ | S <sub>0</sub> |

|-------|-------|-------|-------|-----|-------|----------------|

| 0     | 0     | 0     | 0     | 0   | 0     | 0              |

| 0     | 0     | 0     | 1     | 0   | 0     | 1              |

| 0     | 0     | 1     | 0     | 0   | 1     | 0              |

| 0     | 0     | 1     | 1     | 0   | 1     | 1              |

| 0     | 1     | 0     | 0     | 0   | 0     | 1              |

| 0     | 1     | 0     | 1     | 0   | 1     | 0              |

| 0     | 1     | 1     | 0     | C   | 1     | 1              |

| 0     | 1     | 1     | 1     |     | 0     | 0              |

| 1     | 0     | 0     | 0     | ()  |       | 0              |

| 1     | 0     | 0     | 1     | 0   | 1     | 1              |

| 1     | 0     | 1     | 0     | 1   | 0     | 0              |

| 1     | 0     | 1     | 1     | - 1 | 0     | 1              |

| 1     | 1     | 0     | 0     | 0   |       | 1              |

| 1     | 1     | 0     | 1     |     | 0     | 0              |

| 1     | 1     | 1     | 0     |     | 0     | 1              |

| 1     | 1     | 1     | 1     |     | 7     | 0              |