### Operational Amplifier Frequency Response and Closed-Loop Stability

A real (open-loop) op amp is generally composed of three stages: a moderate-gain differential amplifer stage with high input resistance, a high-gain voltage preamplifier stage, and a unity-gain emitter-follower output stage with low output resistance. Each of these stages has an output resistance and also a ("parasitic", or unwanted) capacitive load. Thus each stage contributes significant voltage or current gain to the overall op amp operation, but also an (unwanted) first-order LPF RC filter section! Thus the voltage gain of a real op amp is NOT independent of frequency, as assumed in our ideal op amp model, but instead the voltage gain of a real op amp decreases with frequency.

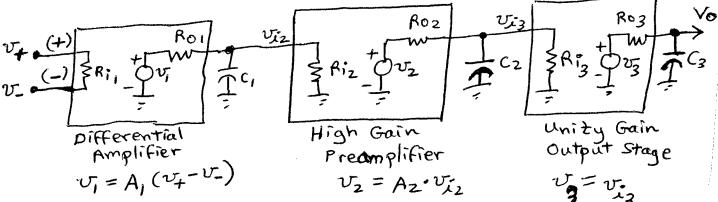

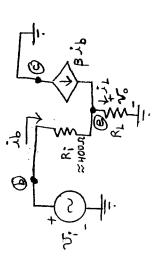

The block diagram of a typical three-stage op amp is

This circuit may be simplified by finding each of the Thevenin equivalent circuits seen "looking out from" the terminals of each capacitor, as shown below:

Earlier in this course we have shown that the simple first-order RC lowpass filter section

has the following transfer function:

$$Av(jf) = \frac{Vo(jf)}{Vi(jf)} = \frac{\frac{1}{(j \cdot 2 \cdot \pi \cdot f \cdot C)}}{\frac{1}{(j \cdot 2 \cdot \pi \cdot f \cdot C)} + R} = \frac{1}{1 + j \cdot 2 \cdot \pi \cdot f \cdot R \cdot C} = \frac{1}{1 + \frac{jf}{f_{break}}}$$

where  $f_{break} = \frac{1}{2 \cdot \pi \cdot R \cdot C}$

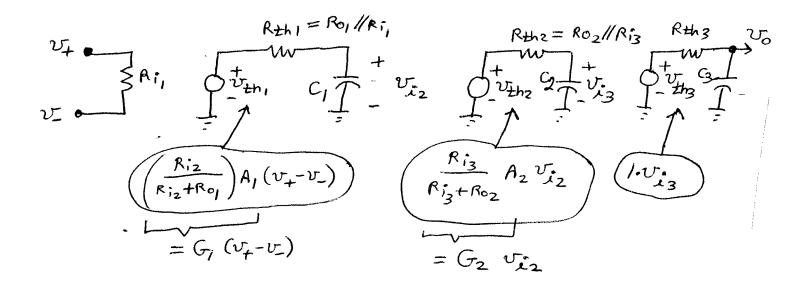

Recall that we ave found that its magnitude and phase Bode plots are

Because the 3-stage op amp consists of a cascade of three first-order LPF sections (with voltage gains in between), its transfer curve must be given by

$$\operatorname{Av}(\operatorname{jf}) = \frac{\operatorname{Vo}(\operatorname{jf})}{\operatorname{Vplus}(\operatorname{jf}) - \operatorname{Vminus}(\operatorname{jf})} = \frac{\operatorname{G}_1 \cdot \operatorname{G}_2 \cdot 1}{\left(1 + \frac{\operatorname{j} \cdot \operatorname{f}}{\operatorname{f}_1}\right) \cdot \left(1 + \frac{\operatorname{j} \cdot \operatorname{f}}{\operatorname{f}_2}\right) \cdot \left(1 + \frac{\operatorname{j} \cdot \operatorname{f}}{\operatorname{f}_3}\right)}$$

where the three break frequencies are

$$f_1 = \frac{1}{2 \cdot \pi \cdot Rth_1 \cdot C_1} \qquad f_2 = \frac{1}{2 \cdot \pi \cdot Rth_2 \cdot C_2} \qquad f_3 = \frac{1}{2 \cdot \pi \cdot Rth_3 \cdot C_3}$$

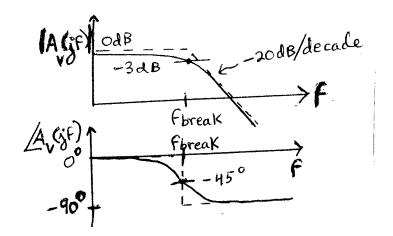

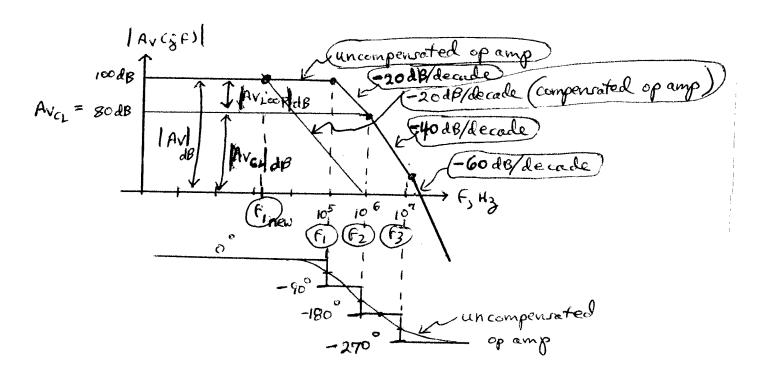

Typically, it is found that  $f_1$  is the smallest, and  $f_3$  is the largest, so the magnitude and phase of the (uncompensated) op amp's transfer function, |Av(jf)| and <Av(jf), may be plotted as the dotted curves shown below:

### Phase and Magnitude Bode Plots for a typical 3-Stage Op Amp

(the uncompensated case is shown by dashed lines and the compensated case is shown by the the solid lines.)

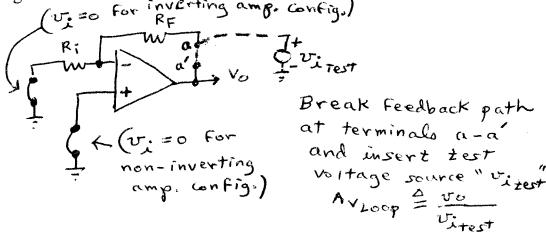

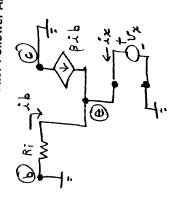

If this (uncompensated) op amp is connected in <u>either</u> the <u>inverting</u> or the <u>non-inverting</u> amplifier configuration, then the gain around the feedback loop (called the "loop gain"  $Av_{LOOP}$ ), may be found using Linear Superposition by setting the external input voltage, vin(t), to zero. This makes the two op amp amplifier configurations <u>identical</u>, as can be seen in the figure below.

The loop gain  $Av_{LOOP}$  is defined by breaking the feedback loop anywhere, say at terminals a - a', and inserting a test voltage source,  $vi_{TEST}$ , between the input terminal and ground and measuring the voltage gain around the broken feedback loop. From the figure above, we see that

$$Av_{LOOP}(jf) = \frac{vo}{vi_{TEST}} = \frac{-R_I}{R_I + R_F} \cdot Av(jf) = -\beta \cdot Av(jf)$$

Where  $\beta = R_I / (R_I + R_F)$  is the voltage gain of the external feedback network that is formed by the resistive voltage divider consisting of resistors  $R_I$  and  $R_F$ , and it is less than unity.  $\beta$  is often referred to as the "return gain". The minus sign must be used to account for the fact that the output is multiplied by  $\beta$  and then fed back into the op amp through its inverting (-) input.

The concept of loop voltage gain is important from a stability standpoint in any "closed-loop" feedback system, because it indicates whether there are any frequencies at which the system will oscillate, which is clearly an undesirable condition in an amplifier!

There are two "Barkhausen conditions" that must simultaneously be satisified if a feedback system is going to oscillate at a given frequency "f":

1. The magnitude of the voltage gain around the loop at frequency "f" must have a magnitude which is equal to or greater than unity. This will allow any sinusoidal noise component at frequency "f" in the circuit (all frequencies are present in the startup transient pulse, as the circuit is first powered up) to become larger and larger as it propagates around the feedback loop and thus small noise sinusoid can build up into a large, sustainable oscillation at frequency "f".

$$\left| Av_{LOOP}(jf) \right| \ge 1$$

2. The phase angle of the voltage gain around the loop at frequency "f" must be an integral multiple of 360 degrees (or  $2\pi$  radians), so that the (sinusoidal) noise that travels around the feedback loop at frequency "f" arrives back at the input <u>in phase</u> with the sinusoidal noise that is already there, so <u>constructive</u> <u>interference</u> will occur and therefore allow oscillations at frequency "f" to build up.

$$<$$

Av<sub>LOOP</sub>(jf) =  $n \cdot 2 \cdot \pi$

Let us consider the standard non-inverting op amp negative-feedback amplifier configuration shown below. (Analysis of the inverting op amp amplifier configuration would proceed in similar fashion and lead to nearly identical results.) The closed-loop voltage gain  $Av_{CL} = vo/vi$  may be found by writing vo in terms of the feedback ("return") gain  $\beta$  as shown:

$$v_{o} = \text{Av} \cdot (\text{vplus} - \text{vminus}) = \text{Av} \cdot (\text{vi} - \beta \cdot \text{v}_{o}) \qquad \text{where} \qquad \beta = \frac{\text{Rin}}{\text{Rin} + \text{R}_{F}}$$

Thus

$$v_{o} \cdot (1 + \text{Av} \cdot \beta) = \text{vi} \cdot \text{Av} \qquad (\beta = \text{"return gain"})$$

Therefore

$$\text{Av}_{CL} = \frac{\text{vo}}{\text{vi}} = \frac{\text{Av}}{1 + \beta \cdot \text{Av}}$$

For  $\beta \cdot \text{Av} >> 1$ ,  $\text{Av}_{CL} = \frac{1}{\beta}$  (Approximately)

Dividing both sides of the inequality above by the return gain,  $\beta$

For Av >>

$$\frac{1}{\beta}$$

= Av<sub>CL</sub>

Thus

Thus as long as the open-loop gain Av is sufficiently greater than  $1/\beta = (Rin + R_F) / Rin$ , which is the closed-loop gain that the op amp has been "strapped for", the actual voltage gain of circuit is fairly accurately predicted by the ideal op amp formula  $Av = (Rin + R_F)/Rin$ . (Perhaps a good rule of thumb is to require Av to be at least 2 times greater than  $Av_{CL}$ .) Note that the closed-loop gain depends mainly on the feedback resistors Rin and  $R_F$  and NOT very much on the open-loop gain Av! This is fortunate, since the feedback resistors Rin and  $R_F$  can be made much more stable (over time, temperature, power supply variations, etc.) than can the open-loop gain of the op amp, Av!

Also note from the result above that for  $\beta*Av >> 1$

$$Av_{CL} = \frac{Av}{1 + \beta \cdot Av} = \frac{A_{V}}{\beta \cdot Av} = \frac{Open\_Loop\_Gain}{|Loop\_Gain|} = \frac{Av}{|Av_{LOOP}|}$$

$$|Av| = |Av_{CL}| \cdot |Av_{LOOP}|$$

frequency "fy" (see the phase plot).

When these voltage gains are expressed in dB (as on a Bode Plot)

$$20 \cdot \log(|Av|) = 20 \cdot \log(|Av_{CL}| \cdot |Av_{LOOP}|) = 20 \cdot \log(|Av_{CL}|) + 20 \cdot \log(|Av_{LOOP}|)$$

$$Av_{dB} = Av_{CLdB} + Av_{LOOPdB}$$

Note from the Bode plot of the uncompensated op amp shown above that if the op amp is strapped for a closed-loop voltage gain of 20 dB (or a gain of 10, with Ri = 1 k $\Omega$  and Ri = 9 k $\Omega$ ), then at a frequency well below the first break frequency f<sub>1</sub>, the closed-loop gain is 20 dB, and the loop gain is 60 dB. However, at the second break frequency, f<sub>2</sub>, the closed-loop gain is still 20 dB, but now the loop gain has fallen to only 20 dB. As we go to higher frequencies, we eventually arrive at frequency fx where the 20 dB horizontal line (representing the desired closed-loop gain) is intercepted by the descending open-loop gain line. At this frequency (fx) the amplifier no longer exhibits a 20 dB closed-loop voltage gain, since the loop gain has fallen to 0 dB (unity gain), and therefore this intercept frequency "fx" approximately represents the high frequency limit of this 20 dB amplifier. However there is a BIG problem with this circuit, because strapping this uncompensated amplifier for a closed-loop voltage gain that is too low (such as 20 dB) makes it oscillate, and thus become unstable! This circuit will break into undesired oscillations at the

This is because the open-loop gain phase plot (<Av) passes through -180 degrees at the frequency fy. Therefore, at this same frequency fy, the phase of the loop gain (<Av $_{LOOP}$ ) must be -180 + (-180) = -360 degrees, since passing through the (-) input of the op amp automatically adds another -180 degrees to the phase of the signal. Furthermore, at this frequency fy, we can see that the magnitude of the loop gain is still >> 1. Therefore, the two Barkhausen criteria are satisfied at frequency fy, and undesired oscillations will therefore develop at this frequency!

But now let us consider strapping the amplifier for a higher closed-loop gain. Say, 40 dB. From the horizontal "40 dB" dotted line on the figure above, we see that the useable bandwidth has been reduced from "fy" to "f2", but now the loop gain is WELL BELOW unity at frequency "fy", where the phase of the open-loop gain of the op amp reaches the "possible oscillation value" of 180 degrees. In fact, because frequency  $f_2$  corresponds to the second break frequency of the op amp, the phase shift at this frequency, which is the frequency where the loop gain  $(Av_{LOOP})$  of the op amp is unity, is only approximately -135 degrees, and thus we are operating with a phase shift at unity gain that is a comfortable 180 - 135 = 45 degrees away from the problem value of 180 degrees! Thus when we strap this uncompensated op amp for a gain of 40 dB, the uncompensated op amp will be stable, with a "phase margin" of 45 degrees. It is always a good idea to operate an amplifer with a suitable phase margin to ensure that subsequent changes in component values due to aging, power supply variation, temperature change, etc. do not allow the circuit to become unstable at a later time.

The op amp may be "compensated" to make it <u>unconditionally stable</u>, no matter what closed-loop gain it is strapped for. Let us consider the worst-case possible feedback situtation from the standpoint of stability considerations, which is when the amplifier is strapped for a closed-loop voltage gain of unity (as in the non-inverting unity-gain voltage follower configuration). Under this condition, the loop gain  $|Av_{LOOP}|$  will be as high as possible, and in fact it is equal to the closed-loop gain magnitude |Av|. Assuming that a 45 degree phase margin is desired, we look at the loop gain of the uncompensated op amp at frequency  $f_2$ , and we see it is 40 dB instead of being equal to or less than unity as desired!)

This problem is solved by adding a compensation capacitor between the output node of the differential amplifier stage of the op amp, in parallel with the parasitic capacitance C<sub>1</sub> that lowers break frequency  $f_1$  down to  $f_{1new}$ , where  $f_{1new}$  is chosen so that the 20 dB/decade slope in the open-loop voltage gain |Av(jf)| reaches unity gain at the second break frequency f<sub>2</sub>. Thus at break frequency f<sub>2</sub>, where the phase has only fallen to -135 degrees, and is thus 45 degrees away from problem frequency "fy" where the phase is -180 degrees, the loop gain has already fallen to unity. Thus there is NO CHANCE of oscillation, no matter what closed-loop gain the amplifier is strapped for since at the 180 degree phase shift frequency, the voltage gain magnitude has to be considerably less than unity. Unfortunately, unconditional stability is bought at the high price of drastically reduced bandwidth of the op amp. Most modern medium-bandwidth op amps are internally compensated, such as the 741 and the TL-072. However, in order to attain wider operating bandwidth, some "high frequency" op amps (such as the TLE2037) are left uncompensated, allowing the user to operate them at higher closed-loop voltage gains, providing that the user adds the appropriate compensating capacitor based upon the closed-loop gain they are strapping the op amp for so that they can operate their amplifer in its stable region with a suitable phase margin.

Note that if the compensated op amp is strapped for a unity closed-loop voltage gain, its useable bandwidth (upper frequency limit) is approximately " $f_2$ ". Therefore, the second break frequency " $f_2$ " is called the "*unity gain bandwidth*" of the op amp, and this value is specified as an op amp parameter in the data sheet of an op amp. Furthermore, since the slope of the open-loop gain |Av(jf)| is approximately -20 dB/decade throughout its useable frequency range, if we strap the amplifer for a closed-loop voltage gain of 10 (20 dB), the bandwidth decreases by 20 dB (a factor of 10) to  $0.1*f_2$ . If we strap it for a closed-loop voltage gain of 100, then the bandwidth (BW) decreases another 20 dB (factor of 10) to  $0.01*f_2$ . Clearly the product of the closed-loop gain and the useable bandwidth of the resulting amplifer must approximately equal  $f_2$ , the unity gain bandwidth.

$$Av_{CL} \cdot BW = f_2 = Unity\_Gain\_BW = Gain\_Bandwidth\_Product$$

For this reason, the "u<u>nity gain bandwidth</u>" parameter of an op amp is also called its "gain-bandwidth product". The published gain-bandwidth product for an LM741 amplifer is 1 MHz, the TL-072 (available from our instrument room) is 3 MHz, and the TLE2037 has a gain-bandwidth product of 85 MHz!

Ex #1: An internally-compensated TL-072 op amp is strapped for a closed-loop voltage gain magnitude of 10, 100, and 1000, using either the inverting or the non-inverting amplifier configuration. It has a gain-bandwidth product of GBW :=  $3 \cdot MHz$ . Find the useable bandwidth (upper frequency limit) in each case:

for

$$Av_{CL} := 10$$

$BW := \frac{GBW}{Av_{CL}}$   $BW = 300 \times 10^3 \, Hz$   $Av_{CL} := 100$   $BW := \frac{GBW}{Av_{CL}}$   $BW = 30 \times 10^3 \, Hz$   $Av_{CL} := 1000$   $BW := \frac{GBW}{Av_{CL}}$   $BW = 3 \times 10^3 \, Hz$

Ex #2: An uncompensated op amp exhibits a dc open-loop voltage gain of Avdc :=  $10^5$  = 100 dB, and has break frequencies f1 :=  $10^5 \cdot \text{Hz}$ , f2 :=  $10^6 \cdot \text{Hz}$ , and f3 :=  $10^7 \cdot \text{Hz}$ . What is the minimum permissible closed-loop voltage gain for which this amplifier may be strapped and still be stable to within a 45 degree phase margin? What is its useable bandwidth at this minimum permissible closed-loop voltage gain? If it is strapped for a gain below this critical level, at what precise frequency will the circuit oscillate?

From the sketch of |Av(jf)| and |Av(jf)| below, we see that  $|Av_{LOOP}|$  falls to 0 dB (unity) at  $f_2 = 1$  MHz, where the |Av(jf)| is approximately 80 - 3 = 77 dB, since at a break frequency ( $f_2$ ), the true gain curve should be approximately 3 dB below the Bode asymptote line.

To find this value more precisely, we may construct its transfer function:

Av(f) =

$$\frac{10^5}{\left(1 + j \cdot \frac{f}{10^5}\right) \cdot \left(1 + j \cdot \frac{f}{10^6}\right) \cdot \left(1 + j \cdot \frac{f}{10^7}\right)}$$

Angle\_Av(f) :=

$$-atan\left(\frac{f}{10^5}\right) - atan\left(\frac{f}{10^6}\right) - atan\left(\frac{f}{10^7}\right)$$

Setting this expression equal to -135 degrees =  $-3\pi/4$  radians, and solving for f

$$f = 1.000 \cdot MHz$$

At this frequency, the magnitude of the open loop gain is

Mag\_Av(f) :=

$$\frac{\left(10^{5}\right)}{\left[1. + \left(\frac{f}{10^{5}}\right)^{2}\right]^{\frac{1}{2}} \left[1. + \left(\frac{f}{10^{6}}\right)^{2}\right]^{\frac{1}{2}} \left[1. + \left(\frac{f}{10^{7}}\right)^{2}\right]^{\frac{1}{2}}}$$

At the -135 degree frequency, 1.00 MHz, the magnitude of the open-loop voltage gain is

$$Mag_Av(1.10^6) = 7.001 \times 10^3$$

In decibels,

Mag\_Av\_dB :=

$$20 \cdot \log(7.10^3)$$

Mag\_Av\_dB =  $76.902 \times 10^0$

Thus the true results a quite close to the graphically predicted results.

If strapped for a gain that is considerably less than 77 dB, the amplifier will oscillate at the frequency where the phase shift passes through -180 degrees, this is found by setting the above expression for the phase angle of Av(jf) to  $-\pi$  radians:

$$-\pi = -\operatorname{atan}\left[\frac{f}{\left(1.0 \times 10^{5}\right)}\right] - \operatorname{atan}\left(\frac{f}{1.0 \times 10^{6}}\right) - \operatorname{atan}\left(\frac{f}{1.0 \times 10^{7}}\right)$$

$$f := 3.331 \cdot MHz$$

Ex #3. To make the op amp <u>unconditionally stable</u>, no matter what closed-loop voltage gain it is strapped for, we consider the worst-case situation where the closed loop gain is unity, so the open loop gain is the same as the loop gain. We desire to increase capacitance C1 such that the first break frequency  $f_1$  is lowered so that the magnitude of the open-loop voltage gain at the -135 degree phase shift frequency ( $f_2$ ) is unity.

To calculate this value, replace  $f_1$  by  $f_{1\text{new}}$  in the open-loop gain magnitude expression above. Then, evaluate it at  $f = f_2 = 10^6$  Hz. Finally, set this expression equal to unity and solve for the resulting value of  $f_{1\text{new}}$ .

$$1 = \frac{\left(10^{5}\right)}{\left[1. + \left(\frac{10^{6}}{f_{1new}}\right)^{2}\right]^{\frac{1}{2}} \left[1. + \left(\frac{10^{6}}{10^{6}}\right)^{2}\right]^{\frac{1}{2}} \left[1. + \left(\frac{10^{6}}{10^{7}}\right)^{2}\right]^{\frac{1}{2}}}$$

$$f_{1new} := 14.21 \cdot Hz$$

If Rth1 is 10 k $\Omega$ , then the value of C<sub>1</sub> required to lower the first break frequency to  $f_{1\text{new}} = 14.21 \text{ Hz}$  is

$$C_1 := \frac{1}{2 \cdot \pi \cdot 10 \cdot k\Omega \cdot 14.21 \cdot Hz}$$

$C_1 = 1.12 \times 10^{-6} F$

This is a very large value of capacitance, which would be fairly expensive, and would take up a lot of space on a circuit board.

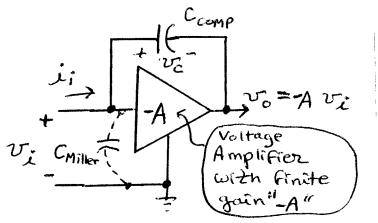

In order to dramatically reduce the size of the compensating capacitor, the concept of "Miller capacitance multiplication" is used. Instead of connecting the compensating capacitor between the output node of the differential amplfier stage and ground (where the original parasitic capacitance C1 is located), the compensation capacitor is placed across the output and input terminals of the preamplifier stage exhibiting finite voltage gain "-A" as shown in the diagram below:

The voltage across the compensating capacitor, vc(t), is

$$vc(t) = \frac{1}{Ccomp} \cdot \int_{-\infty}^{t} i_1 dt$$

But the voltage across the capacitor vc(t) may be expressed in terms of vi(t) since voltage vi(t) appears on the left terminal of Ccomp and voltage Avi(t) appears on the right terminal of the capacitor.

$$vc(t) = vi(t) - (-A \cdot vi(t)) = (1 + A) \cdot vi(t)$$

Thus

$$(1 + A) \cdot vi(t) = \frac{1}{\text{Ccomp}} \cdot \int_{-\infty}^{t} i_1 dt$$

$$vi(t) = \frac{1}{(1+A)Ccomp} \cdot \int_{-\infty}^{t} i_1 dt = \frac{1}{C_{Miller}} \cdot \int_{-\infty}^{t} i_1 dt$$

Thus looking between the input terminal of the amplifier and ground we have an equivalent capacitance (Miller capacitance)  $C_{\text{Miller}} = (1+A)*C_{\text{comp}}$ .

Assuming that the second stage of the op amp (the inverting voltage preamplifier stage) has a voltage gain of -A = -5000, then for  $C_{\text{Miller}} = 1.12 \,\mu\text{F}$ , we require

$$Ccomp = \frac{C_{Miller}}{1 + A}$$

Thus Ccomp need only be 224 pF, which does not take up much space on the circuit board, nor costs very much!

### Op Amp Slew Rate "SR" Specification

We define the slew rate of an OP AMP as the maximum possible rate of change of the OP AMP's output voltage:

$$S_{R} = \left(\frac{d}{dt}v_{0}(t)\right)_{Max}$$

The slew rate of an OP AMP is limited because its output current sourcing/sinking capability is "current-limited" to |lout| < Imax. (For example, for a 741 OP AMP, Imax is limited to 5 mA. For a 411 OP AMP, Imax is limited to 20 mA.)

As the OP AMP's input changes abruptly, the OP AMP's output voltage can only change as fast as its output capacitance ( $C_L$ ) can be charged, which is limited to Imax Coulombs per second. This maximum rate of change if vo(t) is called the OP AMP's slew rate, where

$$I_{MAX} = C_L \cdot \frac{d}{dt} v_0(t)$$

Thus

$$S_R = \left(\frac{d}{dt}v_0(t)\right)_{\text{Max}} = \frac{I_{\text{MAX}}}{C_L}$$

A typical slew rate is 0.6 V/ $\mu$ s for a 741 OP AMP and 15 V/ $\mu$ s for a 411 OP AMP.

### Full Power Frequency Response

While the "small-signal" frequency response of an OP AMP circuit is limited by OP AMP's bandwidth (BW), the "large-signal" response is often limited even further by the slew rate specification of the OP AMP.

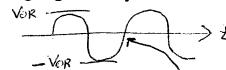

Consider a sinusoidal OP AMP output voltage given by

$$vo(t) = V_{OR} \cdot sin(2 \cdot \pi \cdot f_p \cdot t)$$

Where "VOR" is the maximum rated output voltage, which is usually the full allowable output voltage "swing" usually about 10 V.

And where "fp" is the "full-power response" break frequency, above which vo(t) is no longer able change fast enought to remain sinusoidal.

Taking the derivative of the above expression for vo(t) w.r.t. time yields:

$$\frac{d}{dt}vo(t) = V_{OR} \cdot 2 \cdot \pi \cdot f_p \cdot cos(2 \cdot \pi \cdot f_p \cdot t)$$

Note that  $V_{OR} \cdot 2 \cdot \pi \cdot f_p$  is the maximum value of dvo(t)/dt

Thus,

$$S_R = \left(\frac{d}{dt}v_0(t)\right)_{\mbox{Max}} = V_{OR} \cdot 2 \cdot \pi \cdot f_p$$

Thus

$$f_p = \frac{S_R}{2 \cdot \pi \cdot V_{OR}}$$

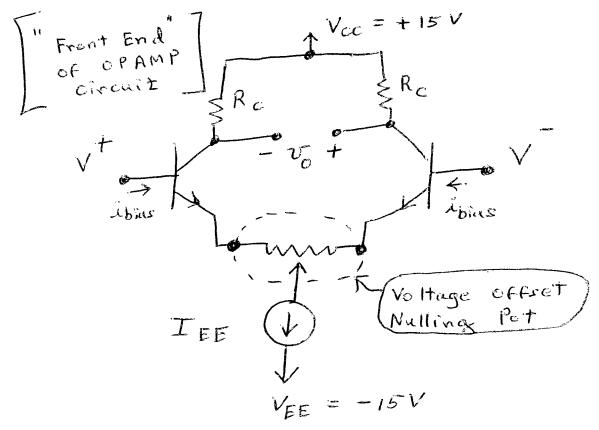

### OP AMP Offset Voltage Nulling

Due to mismatches in the transistors in the differential pair at input of OP AMP,  $I_{EE}$  does not divide equally even when Vplus = Vminus. Thus the output voltage of the differential amplifier, Vo, might differ from zero by as much as 3 mV. As the differential pair changes temperature, there may be an offset voltage drift on the order of 0.1  $\mu$ V/degree C.

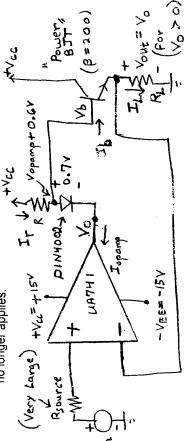

In applications where such an offset voltage is undesired, an offset voltage nulling pot may be added to the circuit, as shown below. It allows mismatches in the transistors to be evened out, so that  $I_{EE}$  divides equally between the two transistors when Vplus = Vminus.

V+15=0

Output/Input Impedances

## AMPLIFIER CIRCUITS WITH NEGATIVE FEEDBACK OUTPUT IMPEDANCE OF OPERATIONAL

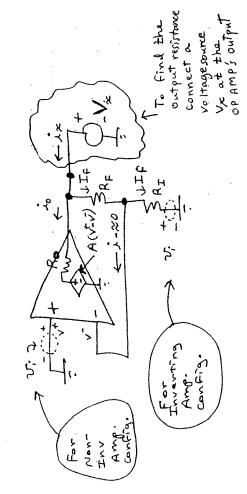

same, as shown in the circuit below. Next we connect a voltage source superposition by reducing the input voltage (Vi) to zero. Then both the inverting and non-inverting OP AMP circuit configurations become the determine the current (ix) that flows through source Vx into the output terminal. Then the equivalent output resistance of the circuit, Rout, is To find the output impedance of an OP AMP circuit, we employ linear (Vx) between the circuit's output terminal and ground, and then we

$$Rout = \frac{Vx}{lx} \left| \frac{V}{U_x} = C \right| \tag{1}$$

Circuit used to Caiculate Output Impedance of OP AMP with Negative Feedback

Analysis holds for both the inverting and hon-inventing OP # MP Configurations. Note: by setting V. = 0 >

EE566/BE550

Page 2

Output/Input Impedances

Using KCL at the output node,

Ix = lo + If

(2)

But lo can be calculated in terms of Vx:

$$I_{0\pi} \frac{V_X - A \cdot (Vplus - Vminus)}{Ro}$$

(3)

Vplus = 0 (This pin is grounded) Where

And Vminus\*

$$\frac{R_i}{R_i + R_f}$$

Vx

Making these substitutions, (3) becomes

$$V_{X} - A \cdot \left(0 - \frac{Ri}{Ri + Rf} \cdot V_{X}\right)$$

(4)

Simplifiying (4) yields

$$lo_{\mathbf{x}} V_{\mathbf{X}} \frac{(R_{\mathbf{i}} + Rf + A \cdot R_{\mathbf{i}})}{((R_{\mathbf{i}} + Rf) \cdot R_{\mathbf{0}})}$$

(5)

if can be calculated from Vx,

$$If_{=} \frac{V_{x}}{Rf + Ri}$$

9

Substituting (5) and (6) into (2) yields

91

EE588/BE550

Page 3

rage 3 Output/Input impedances  $Ix = V_{X^*} \cdot \frac{(Ri + Rf + A \cdot Ri + Ro)}{}$

3

The OP AMP circuit's output impedance is

((Ri + Rf)·Ro)

$$Rout = Vx$$

$$Ix$$

$$V_i \approx 0$$

Let the voltage division ratio of the external negative feedback resistor network be defined as the "return ratio"  $\beta$

$$\beta = \frac{Ri}{Ri + Rf}$$

Then  $Rout = \frac{Ro}{1 + A \cdot \beta + \frac{Ro}{Di \cdot Di}}$  (8)

Assuming that Ro is much less than (Ri+Rf), (8) simplifies to

$$Rout = \frac{Ro}{1 + A \cdot \beta}$$

(9)

Thus the output resistance of the op amp strapped with negative feedback is EVEN LOWER THAN the output resistance of the open-loop OP AMP (Ro), which is already quite low! The output resistance of the overall circuit is approximately Ro divided by the magnitude of the loop gain, Aß (for large loop gains).

As an example, consider an inverting amplifier made with an op amp whose output resistance Ro = 25 ohms, open loop gain A =  $10^{4}$ , and strapped for a gain of 100 ( $\beta$  = 0.01). Then

But remember that the op amp is current limited to about 25 mA!

BUT REMEMBER THAT THE OP AMP IS INTERNALLY CURRENT-LIMITED TO ABOUT + OR - 25 MA, THEREFORE SMALL LOAD RESISTANCES (LESS THAN ABOUT 10V/25MA = 400 . A. CANNOT BE DRIVEN!

Inv. Config. (Rin = Ri)

EE566/BE550

Page 4

Output/Input Impedances

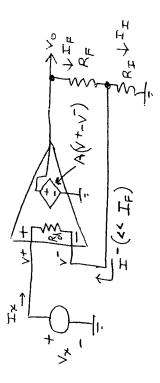

## Input Impedance of Non-inverting OP AMP Configuration (Voltage Follower with Gain)

While the inverting op-amp amplifier circuit has an input impedance that is approximately equal to the value of input resistor Ri (since virtual ground exists on the other side of Ri), the input resistance of the non-inverting configuration is not so obvious.

Because the (+) input connects to virtual ground through the internal differential input resistance of the op amp, Rd, it might appear that the input resistance of this configuration is Rd. However, it will be shown below that the actual input resistance is much greater than this, due to the fact that the voltage across Rd is amplified and fed back to the (-)

As shown below, imagine that a voltage source (Vx) is applied between the input terminal and ground, and the current through this source is Ix, then the input resistance of the amplifying circuit is

$$Rin = \frac{V_X}{I_X} \tag{1}$$

## CIRCUIT USED TO FIND THE INPUT IMPEDANCE OF A NON-INVERTING OP AMP AMPLIFIER CIRCUIT

EES66/BESS0

Page 5

Output/Input Impedances

$^{\rm lx}$  can be calculated in terms of  $\rm Vx$  and Vminus:

$$Ix = \frac{Vx - Vminus}{Rd}$$

(11)

If we assume that Iminus is neglibigie compared to If, then If ≈ Ii, and we can use the voltage divider equation to find the approximate value of Vminus:

$$V_{\text{minus}} \underset{Rf + Ri}{\sim} V_0 \tag{12}$$

Furthermore, Vo can be found in terms of Vx (= Vplus) and

$$Vo = A \cdot (Vplus - Vminus) = A \cdot (Vx - Vminus)$$

(13)

Substituting (13) into (12) yields

Vminus\*

$$\frac{Ri}{(Rf + Ri)} \cdot A \cdot (Vx - Vminus)$$

(14)

Solving (14) for Vminus yields

Vminus=Vx·Ri·

$$\frac{A}{(Rf + Ri + Ri \cdot A)} = \frac{A \cdot \frac{Ri}{Rf + Ri}}{1 + \frac{Ri}{Rf + Ri}} \cdot V_X$$

(15)

attenuation of the external resistive feedback network,  $\beta$ Using the definition of "RETURN RATIO", the voltage

EE566/BE550

Vminus= A·B Vx

Page 6

Output/Input Impedances

2 Where

β\* Rf + Ri

(16)

Substituting this result into (11)

$$I_{X} = \underbrace{\begin{bmatrix} V_{X} - A \cdot \frac{\beta}{(1 + A \cdot \beta)} \cdot V_{X} \end{bmatrix}}_{PA}$$

(17)

Thus, the desired result is

$$Rim = \frac{V_X}{I_X} = (1 + A \cdot \beta) \cdot Rd$$

(18)

the loop gain, Ab, (for large loop-gain magnitudes) It is not uncommon for Rd of an OP AMP to be 1 Megohm. Thus, for a already quite large, is effectively multiplied by the magnitude of The input resistance of the open-loop OP AMP (Rd), which is follower strapped for a closed-loop voltage gain of 101 ( $\beta$  = 0.01) and an open loop gain A =  $10^{4}$ 5, then

$$Rin = (1 + A \cdot \beta) \cdot Rd = (1 + 10^5 \cdot 0.01) \cdot 10^6$$

= 1 Gigohm! Rin = 1.01·10<sup>9</sup>

shunting resistance of the package and the circuit board However, in a real circuit, the input resistance will most certainly be considerably lower than this, since the insulation will be lower than 1 Gigohm!

EE566/BE550

Page 1

Power OP AMPs

## POWER OPERATIONAL AMPLIFIERS

Recall that the typical OP AMP is current-limited to about + or - 25 mA. This implies that, even though the output resistance of an OP AMP amplifier circuit with negative feedback is very low, low load resistances still cannot be driven, due to the OP AMP's output current limiting circuitry, which protects the OP AMP from burning out, since large currents would require large quantities of heat to be dissipated inside the OP AMP.

This output current limitation can be overcome by adding an external complementary symmetry output current booster circuit, which is formed using two resistors, two diodes, and an npn and a pnp power transistor (both are mounted on "heatsinks"). The BJTs are both connected in an "emitter follower" configuration to drive even a relatively low-valued load resistance RL to the op amp output voltage.

This operation of this circuit is based upon the fact that the output voltage of an emitter follower stage follows the input voltage (minus the 0.7 V b-e junction drop), but it has a high input impedance (about  $\beta^*RL$ ), and a low output impedance (about Rb/ $\beta$ ) where  $\beta$  is the forward-current transfer ratio parameter of the transistor, with a typical value of 250.

First, we shall review the operation of the basic npn BJT emitter follower amplifier stage whose circuit and equivalent circuit model are shown below:

CKt Vcc Model Vcc Fud-Active Model

Riztor

Ri

EE566/BE550

Page 2

Power OP AMPs

I. Analysis of BJT Emitter Follower Stage

Part 1. Finding the Output Voltage of an Emitter Follower, Vo

$$Ib_* \frac{V_i - 0.7 - V_0}{R_i}$$

(1)

$$\mathbb{L}_{\bullet} \mathbb{b}(1 \cdot \beta) \tag{2}$$

$\mathfrak{S}$

Substituting (1) and (2) into (3) yields

$$Vo = RL \cdot \frac{Vi - 0.7 - Vo}{Ri} \cdot (1 + \beta)$$

(4)

Solving (4) for Vo yields

$$Vo_{\bullet}RL_{\cdot}\frac{\left(Vi_{\cdot}(\beta+1)\right)-.7\cdot(\beta+1)}{\left(Ri_{\cdot}+RL_{\cdot}(\beta+1)\right)} \tag{5}$$

As long as Ri << RL( $\beta$ +1), which is usually true since  $\beta$  is large, Ri can be ignored, and then (5) dramatically reduces to

Thus the output voltage "follows" the input voltage (minus the 0.7 V b-e junction drop).

The ac voltage gain is 1, therefore what use is this circuit? The answer lies in its low output resistance, Rin, and high input resistance Rout.

EE566/BE550

Page 3

Part 2. Finding the Input Resistance of an Emitter Follower Stage

Because the input resistance Rin is an "ac" parameter defined as "the of superposition to construct the "ac small-signal" circuit model shown change in Vin divided by the change in Ib", we must use the principle model to be reduced to zero. The lowercase symbols ib(t) and vo(t) represent only the time-varying "ac" components of the base current and output voltage, with the constant "dc" components of Ib and Vo below, which requires that the 0.7 V dc source in the above circuit

## AC Small-Signal Model of Emitter Follower Ckt

input voltage Vi, vi, to the changing (ac) part of the input current lb, ib. Thus the input resistance is the ratio of the changing (ac) part of the

Working as before, we see that

8

$$vo = RL \cdot ib \cdot (\beta + 1)$$

and

6)

EE566/BE550

Substituting (8) into (9) yields

Page 4

Power OP AMPs

(10) $vo = RL \cdot \frac{(vi - vo)}{2} \cdot (\beta + 1)$

Solving for vo yields

$$vo \bullet RL \cdot vi \cdot \frac{(\beta + 1)}{(Ri + RL \cdot (\beta + 1))} \tag{11}$$

Substituting (11) into (8) yields

$$v_i$$

-  $RL \cdot v_i$   $(\beta + 1)$

$ib_{\bullet}$   $Ri$

Solving for vi,

$$vi = ib \cdot (Ri + RL \cdot (\beta + 1))$$

(12)

(13)  $Rin_{}=\frac{v_{i}^{\prime }}{ib}=Ri+RL\cdot (\beta +1)$ Thus

If we make the same assumption as before, Ri << RL( $\beta$ +1), we find that the input resistance of the emitter follower stage is approximately given by

$$Rin = RL \cdot (\beta + 1) \tag{14}$$

Since  $\beta$  is large, this input impedance is usually very high.

०र

EE566/BE550

Page 5

Power OP AMPs

Part 3. Finding the Output Resistance of an Emitter Follower Stage

To find the equivalent output resistance looking back from the output terminals where RL has been connected, we may set the input signal source vi to 0, and replace RL by a voltage source, vx that passes source current ix. This circuit is shown in the space below.

### Circuit for Deriving the Equivalent Output Resistance of an Emitter-Follower Amplifier

Then the equivalent output resistance, Rout, is given by

$$Rout = \frac{vx}{ix}$$

(15)

KVL applied around the input loop =>

$$ib_{\bullet \bullet} \frac{0 - vx}{Ri} \tag{16}$$

EE566/BE550 Page 6

Power OP AMPs

KCL applied at the emitter node =>

$$ix = -(\beta + 1) \cdot ib$$

(17)

Substituting (16) into (17) yields

$$ix_{\bullet} - (\beta + 1) \cdot \frac{0 - vx}{Ri}$$

(18)

Thus

$$Rout_{ix} = \frac{vx}{\beta + 1}$$

(19)

Since  $\beta$  is large, this output impedance is usually quite low.

# II. Use of an npn Emitter Follower to Connect a Current-limited OP AMP to a High-current Load

The OP AMP in the circuit below is connected to an external npn emitter-follower output stage. This circuit contains a 0.7 V diode level-shifting circuit that uses a forward-biased diode to cancel out the BJT's 0.7 V b-e internal junction drop. Thus Vout = Vo, assuming that Vcc > Vo, and Vo is kept positive. If Vo goes negative, the npn BJT b-e junction becomes reverse biased and the BJT enters "cut-off", where the controlled source BJT model no longer applies.

Page 7

Power OP AMPs

There are two considerations that influence the choice of bias resistor R. These are best illustrated by an example. Imagine that RL = 8 ohms, which must be driven to values between 0 and 10V. Then Vcc must be comfortably greater than the top end of this range, say Vcc = 15 V. The power transistor has a  $\beta$  of 200. The OP AMP is current-limited to + or - 25 mA.

Consideration 1: Consider the case when the OP AMP is driven to the top end of its range,

And

$$\operatorname{Ir}_{*} \frac{\operatorname{Vcc} - \operatorname{Vb}}{R} > \operatorname{Ib}_{*} \frac{\operatorname{IL}}{(\beta + 1)}$$

$\beta = 200$

So that some residual current is available to flow through the diode to keep it forward biased, thus lopamp is very small.

Rmax =

$$\frac{(Vcc \cdot \beta + Vcc - Vb \cdot \beta - Vb)}{r}$$

Rmax = 691.44 Ohms

### Consideration 2

When Vo = 0V, the current Ib = 0, and all of the current through Ir goes through the op amp. Since the op amp is current limited to 25 mA.

$$\frac{\text{Vcc} - 0.7}{\text{Rmin}} = 0.025$$

Rmin = 572 Ohms

Conclusion: Pick R = 620 ohms

EE566/BE550

Page 8

Power OP AMPs

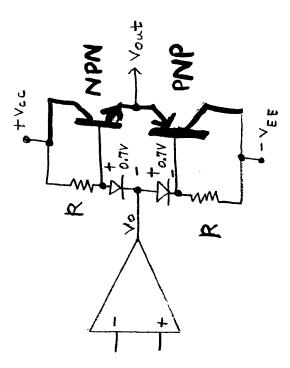

# III. The Complementary Symmetry Output Stage

The circuit above only operates for positive values of output voltage. In order to allow both positive and negative values of output voltage, the following "complementary symmetry" circuit (as shown in our textbook) may be used:

When Vi > 0, the npn BJT is forward active, and the pnp BJT is cut off. When Vi < 0, and pnp BJT is forward active, and the npn BJT is cut off.

NOTE: This entire circuit can be thought of as a power OP AMP, so if it were used in a non-inverting or inverting amplifying configuration, the feedback resistor would typically connect to the junction of the two BJT emitters, rather than the OP AMP output.

Fxample Pewer OP AMP National Semicenductor LM12 - 125W maximum