# PIM\_9A128 Block Guide V01.01

Original Release Date: 8 MARCH 2002 Revised: 30 APRIL 2002

Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and was registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

©Motorola, Inc., 2002

### **Revision History**

| Version<br>Number | Revision<br>Date | Effective<br>Date | Author | Description of Changes                                              |

|-------------------|------------------|-------------------|--------|---------------------------------------------------------------------|

| V01.00            | 8 MAR<br>2002    |                   |        | Initial release                                                     |

| V01.01            | 30 APRIL<br>2002 |                   |        | Corrected bit 6 of Module Routing Register (Figure 3-21 on page 30) |

### **Table of Contents**

| Secti | ion 1 Introduction                   |

|-------|--------------------------------------|

| 1.1   | Overview                             |

| 1.2   | Features                             |

| 1.3   | Block Diagram                        |

| Secti | ion 2 External Signal Description    |

| 2.1   | Overview                             |

| 2.2   | Signal Properties                    |

| Secti | ion 3 Memory Map/Register Definition |

| 3.1   | Register Descriptions                |

| 3.1.1 | Port T Registers                     |

| 3.1.2 | Port S Registers                     |

| 3.1.3 | Port M Registers26                   |

| 3.1.4 | Port P Registers                     |

| 3.1.5 | Port H Registers35                   |

| 3.1.6 | Port J Registers                     |

| Secti | ion 4 Functional Description         |

| 4.1   | General43                            |

| 4.1.1 | I/O Register                         |

| 4.1.2 | Input Register43                     |

| 4.1.3 | Data Direction Register              |

| 4.1.4 | Reduced Drive Register44             |

| 4.1.5 | Pull Device Enable Register          |

| 4.1.6 | Polarity Select Register             |

| 4.2   | Port T                               |

| 4.3   | Port S                               |

| 4.4   | Port M                               |

| 4.4.1 | Module Routing Register              |

| 4.5   | Port P                               |

| 4.6   | Port H                               |

| 4.7   | Port J                               |

| Block 0 | Guide — S12A128PIMV FREE SCAIE Semiconductor, Inc. |

|---------|----------------------------------------------------|

| 4.8     | Port A, B, E, K, and BKGD pin                      |

| 4.9     | External Pin Descriptions                          |

| 4.10    | Low Power Options                                  |

| 4.10.1  | Run Mode48                                         |

| 4.10.2  | Wait Mode                                          |

| 4.10.3  | Stop Mode                                          |

| Secti   | on 5 Resets                                        |

| 5.1     | General49                                          |

| 5.2     | Reset Initialization                               |

|         | on 6 Interrupts                                    |

| 6.1     | General51                                          |

| 6.2     | Interrupt Sources                                  |

| 6.3     | Recovery from STOP                                 |

### **List of Figures**

| Figure 1-1  | PIM_9A128 Block Diagram                   | 12 |

|-------------|-------------------------------------------|----|

| Figure 3-1  | Port T I/O Register (PTT)                 | 20 |

| Figure 3-2  | Port T Input Register (PTIT)              | 20 |

| Figure 3-3  | Port T Data Direction Register (DDRT)     | 21 |

| Figure 3-4  | Port T Reduced Drive Register (RDRT)      | 21 |

| Figure 3-5  | Port T Pull Device Enable Register (PERT) | 22 |

| Figure 3-6  | Port T Polarity Select Register (PPST)    | 22 |

| Figure 3-7  | Port S I/O Register (PTS)                 | 23 |

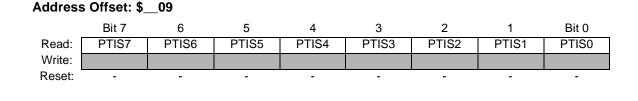

| Figure 3-8  | Port S Input Register (PTIS)              | 23 |

| Figure 3-9  | Port S Data Direction Register (DDRS)     | 24 |

| Figure 3-10 | Port S Reduced Drive Register (RDRS)      | 24 |

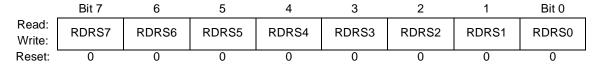

| Figure 3-11 | Port S Pull Device Enable Register (PERS) | 25 |

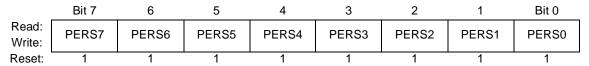

| Figure 3-12 | Port S Polarity Select Register (PPSS)    | 25 |

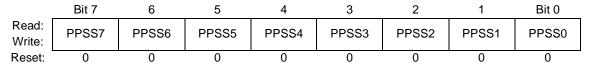

| Figure 3-13 | Port S Wired-OR Mode Register (WOMS)      | 26 |

| Figure 3-14 | Port M I/O Register (PTM)                 | 26 |

| Figure 3-15 | Port M Input Register (PTIM)              | 27 |

| Figure 3-16 | Port M Data Direction Register (DDRM)     | 27 |

| Figure 3-17 | Port M Reduced Drive Register (RDRM)      | 28 |

| Figure 3-18 | Port M Pull Device Enable Register (PERM) | 28 |

| Figure 3-19 | Port M Polarity Select Register (PPSM)    | 29 |

| Figure 3-20 | Port M Wired-OR Mode Register (WOMM)      | 29 |

| Figure 3-21 | Module Routing Register (MODRR)           | 30 |

| Figure 3-22 | Port P I/O Register (PTP)                 | 31 |

| Figure 3-23 | Port P Input Register (PTIP)              | 31 |

| Figure 3-24 | Port P Data Direction Register (DDRP)     | 32 |

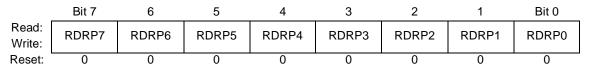

| Figure 3-25 | Port P Reduced Drive Register (RDRP)      |    |

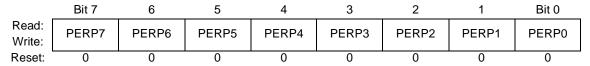

| Figure 3-26 | Port P Pull Device Enable Register (PERP) | 33 |

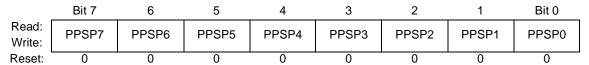

| Figure 3-27 | Port P Polarity Select Register (PPSP)    | 33 |

| Figure 3-28 | Port P Interrupt Enable Register (PIEP)   | 34 |

| Figure 3-29 | Port P Interrupt Flag Register (PIFP)     | 34 |

| Figure 3-30 | Port H I/O Register (PTH)                 |    |

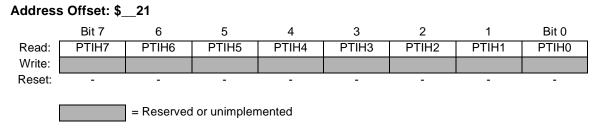

| Figure 3-31 | Port H Input Register (PTIH)              |    |

| Figure 3-32 | Port H Data Direction Register (DDRH)     | 36 |

| Figure 3-33 | Port H Reduced Drive Register (RDRH)                | . 36 |

|-------------|-----------------------------------------------------|------|

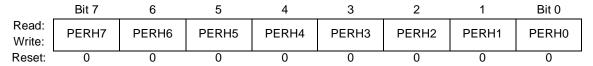

| Figure 3-34 | Port H Pull Device Enable Register (PERH)           | . 37 |

| Figure 3-35 | Port H Polarity Select Register (PPSH)              | . 37 |

| Figure 3-36 | Port H Interrupt Enable Register (PIEH)             | . 38 |

| Figure 3-37 | Port H Interrupt Flag Register (PIFH)               | . 38 |

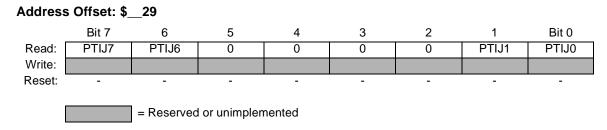

| Figure 3-38 | Port J I/O Register (PTJ)                           | . 39 |

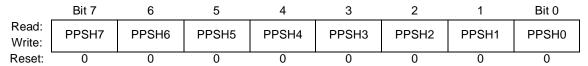

| Figure 3-39 | Port J Input Register (PTIJ)                        | . 39 |

| Figure 3-40 | Port J Data Direction Register (DDRJ)               | . 40 |

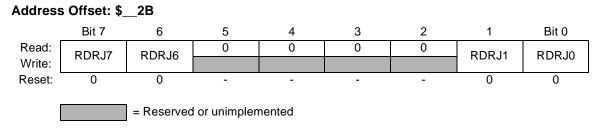

| Figure 3-41 | Port J Reduced Drive Register (RDRJ)                | . 40 |

| Figure 3-42 | Port J Pull Device Enable Register (PERJ)           | . 41 |

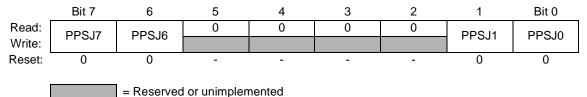

| Figure 3-43 | Port J Polarity Select Register (PPSJ)              | . 41 |

| Figure 3-44 | Port J Interrupt Enable Register (PIEJ)             | . 42 |

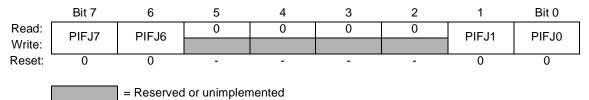

| Figure 3-45 | Port J Interrupt Flag Register (PIFJ)               | . 42 |

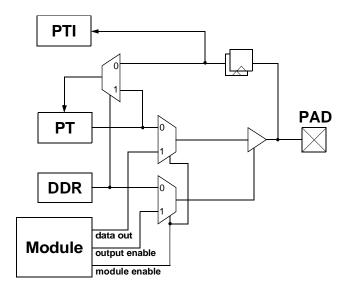

| Figure 4-1  | Illustration of I/O Pin Functionality               | . 44 |

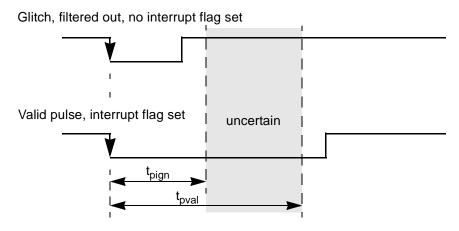

| Figure 4-2  | Interrupt Glitch Filter on Port P, H, and J (PPS=0) | . 46 |

| Figure 4-3  | Pulse Illustration                                  | . 47 |

### **List of Tables**

| Table 0-1 | Acronyms and Abbreviations                  |

|-----------|---------------------------------------------|

| Table 2-1 | Pin Functions and Priorities                |

| Table 3-1 | PIM_9A128 Memory Map                        |

| Table 3-2 | Pin Configuration Summary19                 |

| Table 3-3 | SPI0 Routing                                |

| Table 3-4 | SPI1 Routing                                |

| Table 4-1 | Implemented Modules on Derivatives          |

| Table 4-2 | Pulse Detection Criteria                    |

| Table 5-1 | Port Reset State Summary                    |

| Table 6-1 | Port Integration Module Interrupt Sources51 |

### **Preface**

### **Terminology**

Table 0-1 Acronyms and Abbreviations

| PIM  | Port integration module         |  |  |

|------|---------------------------------|--|--|

| GPIO | General purpose input/output    |  |  |

| SCI  | Serial communications interface |  |  |

| SPI  | Serial peripheral interface     |  |  |

| IIC  | Inter-integrated circuit        |  |  |

| PWM  | Pulse-width modulation          |  |  |

### **Section 1 Introduction**

### 1.1 Overview

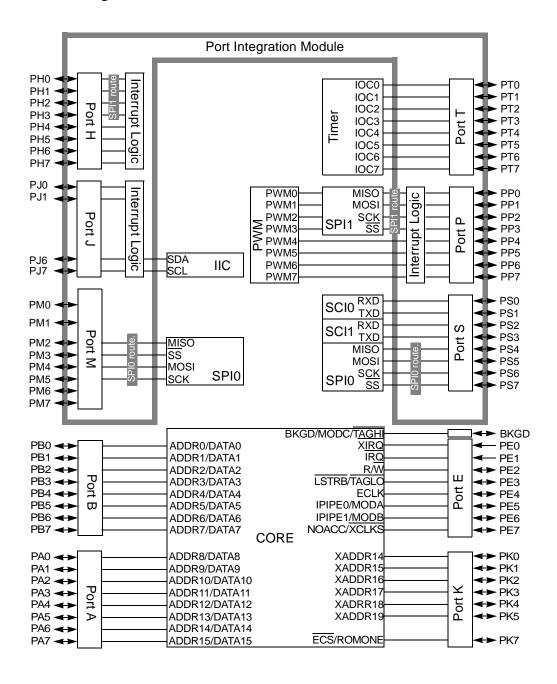

The Port Integration Module establishes the interface between the peripheral modules and the I/O pins for all ports except AD0 and AD1.

**NOTE:** Port A, B, E, and K are related to the core logic and multiplexed bus interface. Refer to the HCS12 Core User Guide (Motorola order number, HCS12COREUG/D) for details.

#### This section covers:

- Port T connected to the timer module

- The serial port S associated with 2 SCI and 1 SPI modules

- Port P connected to the PWM and 1 SPI modules, which also can be used as an external interrupt source

- The standard I/O ports H and J associated with the IIC interface. These ports can also be used as external interrupt sources.

- Port M is associated with 1 SPI module and also used for general purpose I/O

Each I/O pin can be configured by several registers in order to select data direction and drive strength, to enable and select pull-up or pull-down resistors. On certain pins also interrupts can be enabled which result in status flags.

The I/Os of both SPI modules can be routed from their default location to pre-determined pins.

The implementation of the Port Integration Module is device dependent.

### 1.2 Features

A standard port pin has the following minimum features:

- Input/output selection

- 5V output drive with two selectable drive strengths

- 5V digital and analog input

- Input with selectable pull-up or pull-down device

#### Optional features:

- Open drain for wired-or connections

- Interrupt inputs with glitch filtering

### 1.3 Block Diagram

Figure 1-1 is a block diagram of the PIM\_9A128.

Figure 1-1 PIM\_9A128 Block Diagram

### **Section 2 External Signal Description**

### 2.1 Overview

This section lists and describes the signals that do connect off-chip.

### 2.2 Signal Properties

**Table 2-1** shows all the pins and their functions that are controlled by the PIM\_9A128. If there is more than one function associated with a pin, the priority is indicated by the position in the table from top (highest priority) to down (lowest priority).

**Table 2-1 Pin Functions and Priorities**

| Port   | Pin Name | Pin Function<br>& Priority | Description                                                                                           | Pin<br>Function<br>after Reset |          |                                        |      |

|--------|----------|----------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------|----------|----------------------------------------|------|

| Port T | PT[7:0]  | DT[7:0]                    | DT[7:0]                                                                                               | DT[7:0]                        | IOC[7:0] | Enhanced Capture Timer Channels 7 to 0 | GPIO |

| FOIL   |          | GPIO                       | General-purpose I/O                                                                                   | GFIO                           |          |                                        |      |

|        | PS7      | SS0                        | Serial Peripheral Interface 0 slave select output in master mode, input in slave mode or master mode. |                                |          |                                        |      |

|        |          | GPIO                       | General-purpose I/O                                                                                   |                                |          |                                        |      |

|        | PS6      | SCK0                       | Serial Peripheral Interface 0 serial clock pin                                                        |                                |          |                                        |      |

|        | P56      | GPIO                       | General-purpose I/O                                                                                   |                                |          |                                        |      |

|        | PS5      | MOSI0                      | Serial Peripheral Interface 0 master out/slave in pin                                                 |                                |          |                                        |      |

| Port S |          | GPIO                       | General-purpose I/O                                                                                   |                                |          |                                        |      |

|        | PS4      | MISO0                      | Serial Peripheral Interface 0 master in/slave out pin                                                 |                                |          |                                        |      |

|        |          | GPIO                       | General-purpose I/O                                                                                   | GPIO                           |          |                                        |      |

|        | PS3      | TXD1                       | Serial Communication Interface 1 transmit pin                                                         |                                |          |                                        |      |

|        |          | GPIO                       | General-purpose I/O                                                                                   |                                |          |                                        |      |

|        | PS2      | RXD1                       | Serial Communication Interface 1 receive pin                                                          |                                |          |                                        |      |

|        | F 32     | GPIO                       | General-purpose I/O                                                                                   |                                |          |                                        |      |

|        | PS1      | TXD0                       | Serial Communication Interface 0 transmit pin                                                         |                                |          |                                        |      |

|        | FSI      | GPIO                       | General-purpose I/O                                                                                   | 1                              |          |                                        |      |

|        | PS0      | RXD0                       | Serial Communication Interface 0 receive pin                                                          |                                |          |                                        |      |

|        | 130      | GPIO                       | General-purpose I/O                                                                                   |                                |          |                                        |      |

# Block Guide — \$12A128PIMV F/D, Rev. cale Semiconductor, Inc.

| Port   | Pin Name          | Pin Function<br>& Priority | Description                                                                                            | Pin<br>Function<br>after Reset |  |

|--------|-------------------|----------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------|--|

|        | PM7               | GPIO                       | General-purpose I/O                                                                                    |                                |  |

|        | PM6               | GPIO                       | General-purpose I/O                                                                                    |                                |  |

|        | PM5               | SCK0                       | Serial Peripheral Interface 0 serial clock pin                                                         |                                |  |

|        | PIVIO             | GPIO                       | General-purpose I/O                                                                                    |                                |  |

|        | PM4               | MOSI0                      | Serial Peripheral Interface 0 master out/slave in pin                                                  | 1                              |  |

|        | PIVI <del>4</del> | GPIO                       | General-purpose I/O                                                                                    |                                |  |

| Port M | PM3               | SS0                        | Serial Peripheral Interface 0 slave select output in master mode, input for slave mode or master mode. | GPIO                           |  |

|        |                   | GPIO                       | General-purpose I/O                                                                                    |                                |  |

|        | DMO               | MISO0                      | Serial Peripheral Interface 0 master in/slave out pin                                                  |                                |  |

|        | PM2               | GPIO                       | General-purpose I/O                                                                                    |                                |  |

|        | PM1               | GPIO                       | General-purpose I/O                                                                                    |                                |  |

|        | PM0               | GPIO                       | General-purpose I/O                                                                                    |                                |  |

|        | PP7               | PWM7                       | Pulse Width Modulator channel 7                                                                        |                                |  |

|        |                   | GPIO/KWP7                  | General-purpose I/O with interrupt                                                                     |                                |  |

|        | PP6               | PWM6                       | Pulse Width Modulator channel 6                                                                        |                                |  |

|        |                   | GPIO/KWP6                  | General-purpose I/O with interrupt                                                                     |                                |  |

|        | PP5               | PWM5                       | Pulse Width Modulator channel 5                                                                        |                                |  |

|        | FFS               | GPIO/KWP5                  | General-purpose I/O with interrupt                                                                     |                                |  |

|        | PP4               | PWM4                       | Pulse Width Modulator channel 4                                                                        |                                |  |

|        | FF4               | GPIO/KWP4                  | General-purpose I/O with interrupt                                                                     |                                |  |

|        |                   | PWM3                       | Pulse Width Modulator channel 3                                                                        |                                |  |

| Port P | PP3               | SS1                        | Serial Peripheral Interface 1 slave select output in master mode, input for slave mode or master mode. | GPIO                           |  |

|        |                   | GPIO/KWP3                  | General-purpose I/O with interrupt                                                                     |                                |  |

|        |                   | PWM2                       | Pulse Width Modulator channel 2                                                                        |                                |  |

|        | PP2               | SCK1                       | Serial Peripheral Interface 1 serial clock pin                                                         | 1                              |  |

|        |                   | GPIO/KWP2                  | General-purpose I/O with interrupt                                                                     |                                |  |

|        |                   | PWM1                       | Pulse Width Modulator channel 1                                                                        |                                |  |

|        | PP1               | MOSI1                      | Serial Peripheral Interface 1 master out/slave in pin                                                  |                                |  |

|        |                   | GPIO/KWP1                  | General-purpose I/O with interrupt                                                                     |                                |  |

|        |                   | PWM0                       | Pulse Width Modulator channel 0                                                                        |                                |  |

|        | PP0               | MISO1                      | Serial Peripheral Interface 1 master in/slave out pin                                                  |                                |  |

|        |                   | GPIO/KWP0                  | General-purpose I/O with interrupt                                                                     |                                |  |

# Freescale Semiconductor, Inc. S12A128PIMV1/D, Rev. 1

| Port   | Pin Name | Pin Function<br>& Priority                                                                            | Description                                           | Pin<br>Function<br>after Reset |  |

|--------|----------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|--|

|        | PH7      | GPIO/KWH7                                                                                             | General-purpose I/O with interrupt                    |                                |  |

|        | PH6      | GPIO/KWH6                                                                                             | General-purpose I/O with interrupt                    |                                |  |

|        | PH5      | GPIO/KWH5                                                                                             | General-purpose I/O with interrupt                    |                                |  |

|        | PH4      | GPIO/KWH4                                                                                             | General-purpose I/O with interrupt                    |                                |  |

| Port H | PH3      | Serial Peripheral Interface 1 slave select output in master mode input for slave mode or master mode. |                                                       | GPIO                           |  |

|        |          | GPIO/KWH3 General-purpose I/O with interrupt                                                          |                                                       |                                |  |

|        | PH2      | SCK1                                                                                                  | Serial Peripheral Interface 1 serial clock pin        |                                |  |

|        |          | GPIO/KWH2                                                                                             | General-purpose I/O with interrupt                    |                                |  |

|        | PH1      | MOSI1                                                                                                 | Serial Peripheral Interface 1 master out/slave in pin |                                |  |

|        | РПІ      | GPIO/KWH1                                                                                             | General-purpose I/O with interrupt                    |                                |  |

|        | PH0      | MISO1                                                                                                 | Serial Peripheral Interface 1 master in/slave out pin |                                |  |

|        | FNU      | GPIO/KWH0                                                                                             | General-purpose I/O with interrupt                    |                                |  |

|        | PJ7      | SCL                                                                                                   | Inter Integrated Circuit serial clock line            |                                |  |

|        | FJ/      | GPIO/KWJ7                                                                                             | General-purpose I/O with interrupt                    |                                |  |

| Port J | PJ6      | SDA                                                                                                   | Inter Integrated Circuit serial data line             | GPIO                           |  |

|        | FJ0      | GPIO/KWJ6 General-purpose I/O with interrupt                                                          |                                                       |                                |  |

|        | PJ[1:0]  | GPIO/KWJ[1:0]                                                                                         | General-purpose I/O with interrupt                    |                                |  |

### **Section 3 Memory Map/Register Definition**

This section provides a detailed description of all registers.

**Table 3-1** shows the register map of the Port Integration Module.

Table 3-1 PIM\_9A128 Memory Map

| Table 3-1 PIW_9A128 Memory Map |                                           |        |  |  |

|--------------------------------|-------------------------------------------|--------|--|--|

| Address offset                 | Use                                       | Access |  |  |

| \$00                           | Port T I/O Register (PTT)                 | RW     |  |  |

| \$01                           | Port T Input Register (PTIT)              | R      |  |  |

| \$02                           | Port T Data Direction Register (DDRT)     | RW     |  |  |

| \$03                           | Port T Reduced Drive Register (RDRT)      | RW     |  |  |

| \$04                           | Port T Pull Device Enable Register (PERT) | RW     |  |  |

| \$05                           | Port T Polarity Select Register (PPST)    | RW     |  |  |

| \$06                           | Reserved                                  | -      |  |  |

| \$07                           | Reserved                                  | -      |  |  |

| \$08                           | Port S I/O Register (PTS)                 | RW     |  |  |

| \$09                           | Port S Input Register (PTIS)              | R      |  |  |

| \$0A                           | Port S Data Direction Register (DDRS)     | RW     |  |  |

| \$0B                           | Port S Reduced Drive Register (RDRS)      | RW     |  |  |

| \$0C                           | Port S Pull Device Enable Register (PERS) | RW     |  |  |

| \$0D                           | Port S Polarity Select Register (PPSS)    | RW     |  |  |

| \$0E                           | Port S Wired-OR Mode Register (WOMS)      | RW     |  |  |

| \$0F                           | Reserved                                  | -      |  |  |

| \$10                           | Port M I/O Register (PTM)                 | RW     |  |  |

| \$11                           | Port M Input Register (PTIM)              | R      |  |  |

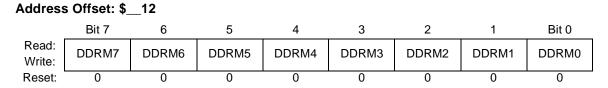

| \$12                           | Port M Data Direction Register (DDRM)     | RW     |  |  |

| \$13                           | Port M Reduced Drive Register (RDRM)      | RW     |  |  |

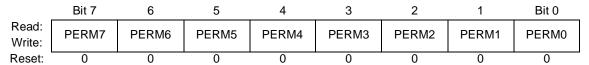

| \$14                           | Port M Pull Device Enable Register (PERM) | RW     |  |  |

| \$15                           | Port M Polarity Select Register (PPSM)    | RW     |  |  |

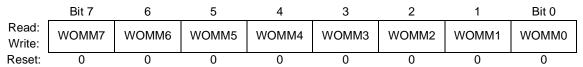

| \$16                           | Port M Wired-OR Mode Register (WOMM)      | RW     |  |  |

| \$17                           | Module Routing Register (MODRR)           | RW     |  |  |

| \$18                           | Port P I/O Register (PTP)                 | RW     |  |  |

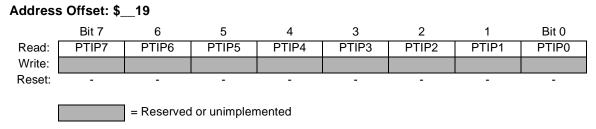

| \$19                           | Port P Input Register (PTIP)              | R      |  |  |

| \$1A                           | Port P Data Direction Register (DDRP)     | RW     |  |  |

| \$1B                           | Port P Reduced Drive Register (RDRP)      | RW     |  |  |

| \$1C                           | Port P Pull Device Enable Register (PERP) | RW     |  |  |

| \$1D                           | Port P Polarity Select Register (PPSP)    | RW     |  |  |

| \$1E                           | Port P Interrupt Enable Register (PIEP)   | RW     |  |  |

| \$1F                           | Port P Interrupt Flag Register (PIFP)     | RW     |  |  |

| \$20                           | Port H I/O Register (PTH)                 | RW     |  |  |

| \$21                           | Port H Input Register (PTIH)              | R      |  |  |

| \$22                           | Port H Data Direction Register (DDRH)     | RW     |  |  |

| \$23                           | Port H Reduced Drive Register (RDRH)      | RW     |  |  |

| \$24                           | Port H Pull Device Enable Register (PERH) | RW     |  |  |

| \$25                           | Port H Polarity Select Register (PPSH)    | RW     |  |  |

| \$26        | Port H Interrupt Enable Register (PIEH)   | RW              |

|-------------|-------------------------------------------|-----------------|

| \$27        | Port H Interrupt Flag Register (PIFH)     | RW              |

| \$28        | Port J I/O Register (PTJ)                 | RW <sup>1</sup> |

| \$29        | Port J Input Register (PTIJ)              | R               |

| \$2A        | Port J Data Direction Register (DDRJ)     | RW <sup>1</sup> |

| \$2B        | Port J Reduced Drive Register (RDRJ)      | RW <sup>1</sup> |

| \$2C        | Port J Pull Device Enable Register (PERJ) | RW <sup>1</sup> |

| \$2D        | Port J Polarity Select Register (PPSJ)    | RW <sup>1</sup> |

| \$2E        | Port J Interrupt Enable Register (PIEJ)   | RW <sup>1</sup> |

| \$2F        | Port J Interrupt Flag Register (PIFJ)     | RW <sup>1</sup> |

| \$30 - \$3F | Reserved                                  | -               |

#### NOTES

**NOTE:** Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

### 3.1 Register Descriptions

The following table summarizes the effect on the various configuration bits, data direction (DDR), output level (I/O), reduced drive (RDR), pull enable (PE), pull select (PS) and interrupt enable (IE) for the ports. The configuration bit PS is used for two purposes:

- 1. Configure the sensitive interrupt edge (rising or falling), if interrupt is enabled.

- 2. Select either a pull-up or pull-down device if PE is active.

Write access not applicable for one or more register bits. Please refer to detailed signal description.

## Freescale Semiconductor, Inc. \_ S12A128PIMV1/D, Rev. 1

**Table 3-2 Pin Configuration Summary**

| DDR | Ю | RDR | PE | PS | IE <sup>1</sup> | Function                   | Pull Device | Interrupt    |

|-----|---|-----|----|----|-----------------|----------------------------|-------------|--------------|

| 0   | Х | Х   | 0  | Х  | 0               | Input                      | Disabled    | Disabled     |

| 0   | Х | Х   | 1  | 0  | 0               | Input                      | Pull Up     | Disabled     |

| 0   | Х | Х   | 1  | 1  | 0               | Input                      | Pull Down   | Disabled     |

| 0   | Х | Х   | 0  | 0  | 1               | Input                      | Disabled    | falling edge |

| 0   | Х | Х   | 0  | 1  | 1               | Input                      | Disabled    | rising edge  |

| 0   | Х | Х   | 1  | 0  | 1               | Input                      | Pull Up     | falling edge |

| 0   | Х | Х   | 1  | 1  | 1               | Input                      | Pull Down   | rising edge  |

| 1   | 0 | 0   | Х  | Х  | 0               | Output, full drive to 0    | Disabled    | Disabled     |

| 1   | 1 | 0   | Х  | Х  | 0               | Output, full drive to 1    | Disabled    | Disabled     |

| 1   | 0 | 1   | Х  | Х  | 0               | Output, reduced drive to 0 | Disabled    | Disabled     |

| 1   | 1 | 1   | Х  | Х  | 0               | Output, reduced drive to 1 | Disabled    | Disabled     |

| 1   | 0 | 0   | Х  | 0  | 1               | Output, full drive to 0    | Disabled    | falling edge |

| 1   | 1 | 0   | Х  | 1  | 1               | Output, full drive to 1    | Disabled    | rising edge  |

| 1   | 0 | 1   | Х  | 0  | 1               | Output, reduced drive to 0 | Disabled    | falling edge |

| 1   | 1 | 1   | Х  | 1  | 1               | Output, reduced drive to 1 | Disabled    | rising edge  |

#### NOTES:

**NOTE:** All bits of all registers in this module are completely synchronous to internal clocks during a register read.

<sup>1.</sup> Applicable only on port P, H and J.

### 3.1.1 Port T Registers

#### Address Offset: \$\_\_00

|                | Bit 7 | 6    | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|----------------|-------|------|------|------|------|------|------|-------|

| Read:<br>Write | PTT7  | PTT6 | PTT5 | PTT4 | PTT3 | PTT2 | PTT1 | PTT0  |

| ECT:           | IOC7  | IOC6 | IOC5 | IOC4 | IOC3 | IOC2 | IOC1 | IOC0  |

| Reset:         | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0     |

Figure 3-1 Port T I/O Register (PTT)

Read: Anytime.

Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

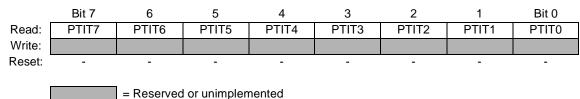

#### Address Offset: \$\_\_01

Figure 3-2 Port T Input Register (PTIT)

Read: Anytime.

Write: Never, writes to this register have no effect.

This register always reads back the status of the associated pins. This can also be used to detect overload or short circuit conditions on output pins.

### Freescale Semiconductor, Inc.— S12A128PIMV1/D, Rev. 1

#### Address Offset: \$ 02

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | DDRT7 | DDRT6 | DDRT5 | DDRT4 | DDRT3 | DDRT2 | DDRT1 | DDRT0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-3 Port T Data Direction Register (DDRT)

Read: Anytime.

Write: Anytime.

This register configures each port T pin as either input or output.

The ECT forces the I/O state to be an output for each timer port associated with an enabled output compare. In these cases the data direction bits will not change.

The DDRT bits revert to controlling the I/O direction of a pin when the associated timer output compare is disabled.

The timer input capture always monitors the state of the pin.

DDRT[7:0] — Data Direction Port T

1 = Associated pin is configured as output.

0 =Associated pin is configured as input.

Due to internal synchronization circuits, it can take up to 2 bus cycles until the correct value is read on PTT or PTIT registers, when changing the DDRT register.

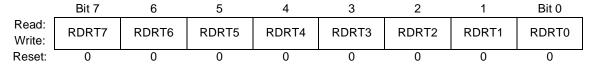

#### Address Offset: \$\_\_03

Figure 3-4 Port T Reduced Drive Register (RDRT)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each port T output pin as either full or reduced. If the port is used as input this bit is ignored.

RDRT[7:0] — Reduced Drive Port T

1 = Associated pin drives at reduced drive strength.

0 =Full drive strength at output.

#### Address Offset: \$\_\_04

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | PERT7 | PERT6 | PERT5 | PERT4 | PERT3 | PERT2 | PERT1 | PERT0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-5 Port T Pull Device Enable Register (PERT)

Read: Anytime.

Write: Anytime.

This register configures whether a pull-up or a pull-down device is activated, if the port is used as input. This bit has no effect if the port is used as output. Out of reset no pull device is enabled.

PERT[7:0] — Pull Device Enable Port T

- 1 = Either a pull-up or pull-down device is enabled.

- 0 = Pull-up or pull-down device is disabled.

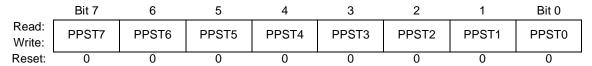

#### Address Offset: \$ 05

Figure 3-6 Port T Polarity Select Register (PPST)

Read: Anytime.

Write: Anytime.

This register selects whether a pull-down or a pull-up device is connected to the pin.

PPST[7:0] — Pull Select Port T

- 1 = A pull-down device is connected to the associated port T pin, if enabled by the associated bit in register PERT and if the port is used as input.

- 0 = A pull-up device is connected to the associated port T pin, if enabled by the associated bit in register PERT and if the port is used as input.

### 3.1.2 Port S Registers

#### Address Offset: \$\_\_08

|                 | Bit 7 | 6    | 5     | 4     | 3    | 2    | 1    | Bit 0 |

|-----------------|-------|------|-------|-------|------|------|------|-------|

| Read:<br>Write: | PTS7  | PTS6 | PTS5  | PTS4  | PTS3 | PTS2 | PTS1 | PTS0  |

| SPI/SCI         | SS0   | SCK0 | MOSI0 | MISO0 | TXD1 | RXD1 | TXD0 | RXD0  |

| Reset:          | 0     | 0    | 0     | 0     | 0    | 0    | 0    | 0     |

Figure 3-7 Port S I/O Register (PTS)

Read: Anytime.

Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

The SPI pins (PS[7:4]) configuration is determined by several status bits in the SPI module. Refer to *HCS12 Serial Peripheral Interface (SCI) Block Guide* (Motorola document order number, S12SPIV2/D) for details.

The SCI ports associated with transmit pins 3 and 1 are configured as outputs if the transmitter is enabled. The SCI ports associated with receive pins 2 and 0 are configured as inputs if the receiver is enabled. Refer to *HCS12 Serial Communications Interface (SCI) Block Guide* (Motorola document order number, S12SCIV2/D) for details.

Figure 3-8 Port S Input Register (PTIS)

= Reserved or unimplemented

Read: Anytime.

Write: Never, writes to this register have no effect.

This register always reads back the status of the associated pins. This also can be used to detect overload or short circuit conditions on output pins.

#### Address Offset:\$ 0A

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | DDRS7 | DDRS6 | DDRS5 | DDRS4 | DDRS3 | DDRS2 | DDRS1 | DDRS0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-9 Port S Data Direction Register (DDRS)

Read: Anytime.

Write: Anytime.

This register configures each port S pin as either input or output

If SPI is enabled, the SPI determines the pin direction. Refer to *HCS12 Serial Peripheral Interface (SPI) Block Guide* (Motorola document order number, S12SPIV2/D) for details.

If the associated SCI transmit or receive channel is enabled this register has no effect on the pins. The pin is forced to be an output if a SCI transmit channel is enabled, it is forced to be an input if the SCI receive channel is enabled.

The DDRS bits revert to controlling the I/O direction of a pin when the associated channel is disabled.

DDRS[7:0] — Data Direction Port S

- 1 = Associated pin is configured as output.

- 0 = Associated pin is configured as input.

Due to internal synchronization circuits, it can take up to 2 bus cycles until the correct value is read on PTS or PTIS registers, when changing the DDRS register.

#### Address Offset: \$ 0B

Figure 3-10 Port S Reduced Drive Register (RDRS)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each port S output pin as either full or reduced. If the port is used as input this bit is ignored.

RDRS[7:0] — Reduced Drive Port S

- 1 = Associated pin drives at reduced drive strength.

- 0 = Full drive strength at output.

## Freescale Semiconductor, Inc.— S12A128PIMV1/D, Rev. 1

#### Address Offset: \$ 0C

Figure 3-11 Port S Pull Device Enable Register (PERS)

Read: Anytime.

Write: Anytime.

This register configures whether a pull-up or a pull-down device is activated, if the port is used as input or as output in wired-or (open drain) mode. This bit has no effect if the port is used as push-pull output. Out of reset a pull-up device is enabled.

PERS[7:0] — Pull Device Enable Port S

- 1 = Either a pull-up or pull-down device is enabled.

- 0 = Pull-up or pull-down device is disabled.

#### Address Offset: \$\_\_0D

Figure 3-12 Port S Polarity Select Register (PPSS)

Read: Anytime.

Write: Anytime.

This register selects whether a pull-down or a pull-up device is connected to the pin.

PPSS[7:0] — Pull Select Port S

- 1 = A pull-down device is connected to the associated port S pin, if enabled by the associated bit in register PERS and if the port is used as input.

- 0 = A pull-up device is connected to the associated port S pin, if enabled by the associated bit in register PERS and if the port is used as input or as wired-or output.

#### Address Offset: \$\_\_0E

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | WOMS7 | WOMS6 | WOMS5 | WOMS4 | WOMS3 | WOMS2 | WOMS1 | WOMS0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-13 Port S Wired-OR Mode Register (WOMS)

Read: Anytime.

Write: Anytime.

This register configures the output pins as wired-or. If enabled the output is driven active low only (open-drain). A logic level of "1" is not driven. It applies also to the SPI and SCI outputs and allows a multipoint connection of several serial modules. This bit has no influence on pins used as inputs.

WOMS[7:0] — Wired-OR Mode Port S

- 1 = Output buffers operate as open-drain outputs.

- 0 = Output buffers operate as push-pull outputs.

### 3.1.3 Port M Registers

#### Address Offset: \$ 10

|                 | Bit 7 | 6    | 5    | 4     | 3    | 2     | 1    | Bit 0 |

|-----------------|-------|------|------|-------|------|-------|------|-------|

| Read:<br>Write: | PTM7  | PTM6 | PTM5 | PTM4  | PTM3 | PTM2  | PTM1 | PTM0  |

| SPI0:           |       |      | SCK0 | MOSI0 | SS0  | MISO0 |      |       |

| Reset           | 0     | 0    | 0    | 0     | 0    | 0     | 0    | 0     |

Figure 3-14 Port M I/O Register (PTM)

Read: Anytime.

Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

#### PM[5:2]

The SPI0 function (SCK0, MOSI0,  $\overline{SS0}$  and MISO0) takes precedence of the general purpose I/O function if the SPI0 is enabled. Refer to *HSC12 Serial Peripheral Interface (SPI) Block Guide* (Motorola document order number S12SPIV2/D) for details.

## Freescale Semiconductor, Inc.— S12A128PIMV1/D, Rev. 1

#### Address Offset: \$ 11 2 Bit 7 6 5 3 Bit 0 4 1 PTIM0 PTIM7 PTIM5 PTIM4 PTIM3 PTIM2 Read: PTIM6 PTIM1 Write: Reset: = Reserved or unimplemented

Figure 3-15 Port M Input Register (PTIM)

Read: Anytime.

Write: Never, writes to this register have no effect.

This register always reads back the status of the associated pins. This can also be used to detect overload or short circuit conditions on output pins.

Figure 3-16 Port M Data Direction Register (DDRM)

Read: Anytime.

Write: Anytime.

This register configures each port M pin as either input or output.

If the SPI0 module is enabled, the SPI determines the pin direction refer to *HCS12 Serial Peripheral Interface (SPI) Block Guide* (Motorola document order number S12SPIV2/D) for details, and this register has no effect.

The DDRM bits revert to controlling the I/O direction of a pin when the SPI0 module is disabled.

DDRM[7:0] — Data Direction Port M

- 1 = Associated pin is configured as output.

- 0 =Associated pin is configured as input.

Due to internal synchronization circuits, it can take up to 2 bus cycles until the correct value is read on PTM or PTIM registers, when changing the DDRM register.

#### Address Offset: \$\_\_13

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | RDRM7 | RDRM6 | RDRM5 | RDRM4 | RDRM3 | RDRM2 | RDRM1 | RDRM0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-17 Port M Reduced Drive Register (RDRM)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each port M output pin as either full or reduced. If the port is used as input this bit is ignored.

RDRM[7:0] — Reduced Drive Port M

1 = Associated pin drives at reduced drive strength.

0 = Full drive strength at output.

#### Address Offset: \$\_\_14

Figure 3-18 Port M Pull Device Enable Register (PERM)

Read: Anytime.

Write: Anytime.

This register configures whether a pull-up or a pull-down device is activated, if the port is used as input or wired-or output. This bit has no effect if the port is used as push-pull output. Out of reset no pull device is enabled.

PERM[7:0] — Pull Device Enable Port M

- 1 = Either a pull-up or pull-down device is enabled.

- 0 = Pull-up or pull-down device is disabled.

### Freescale Semiconductor, Inc.— S12A128PIMV1/D, Rev. 1

#### Address Offset: \$\_\_15

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | PPSM7 | PPSM6 | PPSM5 | PPSM4 | PPSM3 | PPSM2 | PPSM1 | PPSM0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-19 Port M Polarity Select Register (PPSM)

Read: Anytime.

Write: Anytime.

This register selects whether a pull-down or a pull-up device is connected to the pin.

#### PPSM[7:0] — Pull Select Port M

- 1 = A pull-down device is connected to the associated port M pin, if enabled by the associated bit in register PERM and if the port is used as a general purpose input.

- 0 = A pull-up device is connected to the associated port M pin, if enabled by the associated bit in register PERM and if the port is used as general purpose input.

#### Address Offset: \$\_\_16

Figure 3-20 Port M Wired-OR Mode Register (WOMM)

Read: Anytime.

Write: Anytime.

This register configures the output pins as wired-or. If enabled the output is driven active low only (open-drain). A logic level of "1" is not driven. It allows a multipoint connection of several serial modules. This bit has no influence on pins used as inputs.

### WOMM[7:0] — Wired-OR Mode Port M

- 1 = Output buffers operate as open-drain outputs.

- 0 = Output buffers operate as push-pull outputs.

# Block Guide — \$12A128PIMV I/D, Rev. 1

#### Address Offset: \$\_\_17

|        | Bit 7 | 6 | 5       | 4      | 3 | 2 | 1 | Bit 0 |

|--------|-------|---|---------|--------|---|---|---|-------|

| Read:  | 0     | 0 | MODRR5  | MODRR4 | 0 | 0 | 0 | 0     |

| Write: |       |   | WODICKS | WODKK  |   |   |   |       |

| Reset: | 0     | 0 | 0       | 0      | 0 | 0 | 0 | 0     |

|        |       |   |         |        |   |   |   |       |

= Reserved or unimplemented

Figure 3-21 Module Routing Register (MODRR)

Read: Anytime.

Write: Anytime.

This register configures the re-routing of SPI0 and SPI1 on defined port pins.

MODRR[4] — SPI0 Routing

**Table 3-3 SPI0 Routing**

| MODRR[4] | MISO0 | MOSI0 | SCK0 | SS0 |

|----------|-------|-------|------|-----|

| 0        | PS4   | PS5   | PS6  | PS7 |

| 1        | PM2   | PM4   | PM5  | РМ3 |

MODRR[5] — SPI1 Routing

**Table 3-4 SPI1 Routing**

| MODRR[5] | MISO1 | MOSI1 | SCK1 | SS1 |

|----------|-------|-------|------|-----|

| 0        | PP0   | PP1   | PP2  | PP3 |

| 1        | PH0   | PH1   | PH2  | PH3 |

### 3.1.4 Port P Registers

#### Address Offset: \$ 18 Bit 7 6 5 4 3 2 1 Bit 0 Read: PTP7 PTP5 PTP4 PTP3 PTP2 PTP1 PTP6 PTP0 Write: PWM: PWM7 PWM6 PWM5 PWM4 PWM3 PWM2 PWM1 PWM0 SPI: MOSI1 MISO1 SS1 SCK1 Reset: 0 0 0 0 0 0 0 0

Figure 3-22 Port P I/O Register (PTP)

Read: Anytime.

Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

The PWM function takes precedence over the general purpose I/O function if the associated PWM channel is enabled. While channels 6-0 are output only if the respective channel is enabled, channel 7 can be PWM output or input if the shutdown feature is enabled. Refer to HCS12 8-Bit, 8-Channel Pulse Width Modulator (PWM) Block Guide (Motorola document order number S12PWM8B8CV1/D) for details. The SPI function takes precedence over the general purpose I/O function associated with if enabled. Refer to HSC12 Serial Peripheral Interface (SPI) Block Guide (Motorola document order number, S12SPIV2/D) for details.

If both PWM and SPI are enabled the PWM functionality takes precedence.

Figure 3-23 Port P Input Register (PTIP)

Read: Anytime.

Write: Never, writes to this register have no effect.

This register always reads back the status of the associated pins. This can be also used to detect overload or short circuit conditions on output pins.

#### Address Offset: \$\_\_1A

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | DDRP7 | DDRP6 | DDRP5 | DDRP4 | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-24 Port P Data Direction Register (DDRP)

Read: Anytime.

Write: Anytime.

This register configures each port P pin as either input or output.

If the associated PWM channel or SPI module is enabled this register has no effect on the pins. The PWM forces the I/O state to be an output for each port line associated with an enabled PWM7-0 channel. Channel 7 can force the pin to input if the shutdown feature is enabled.

If a SPI module is enabled, the SPI determines the pin direction. Refer to *HCS12 Serial Peripheral Interface (SPI) Block Guide* (Motorola document order number, S12SPIV2/D) for details.

The DDRM bits revert to controlling the I/O direction of a pin when the associated PWM channel is disabled.

DDRP[7:0] — Data Direction Port P

1 = Associated pin is configured as output.

0 =Associated pin is configured as input.

Due to internal synchronization circuits, it can take up to 2 bus cycles until the correct value is read on PTP or PTIP registers, when changing the DDRP register.

#### Address Offset: \$\_\_1B

Figure 3-25 Port P Reduced Drive Register (RDRP)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each port P output pin as either full or reduced. If the port is used as input this bit is ignored.

RDRP[7:0] — Reduced Drive Port P

1 = Associated pin drives at reduced drive strength.

0 =Full drive strength at output.

### Freescale Semiconductor, Inc. S12A128PIMV1/D, Rev. 1

#### Address Offset: \$ 1C

Figure 3-26 Port P Pull Device Enable Register (PERP)

Read: Anytime.

Write: Anytime.

This register configures whether a pull-up or a pull-down device is activated, if the port is used as input. This bit has no effect if the port is used as output. Out of reset no pull device is enabled.

PERP[7:0] — Pull Device Enable Port P

1 = Either a pull-up or pull-down device is enabled.

0 = Pull-up or pull-down device is disabled.

#### Address Offset: \$ 1D

Figure 3-27 Port P Polarity Select Register (PPSP)

Read: Anytime.

Write: Anytime.

This register serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.

PPSP[7:0] — Polarity Select Port P

- 1 = Rising edge on the associated port P pin sets the associated flag bit in the PIFP register.A pull-down device is connected to the associated port P pin, if enabled by the associated bit in register PERP and if the port is used as input.

- 0 = Falling edge on the associated port P pin sets the associated flag bit in the PIFP register. A pull-up device is connected to the associated port P pin, if enabled by the associated bit in register PERP and if the port is used as input.

#### Address Offset: \$\_\_1E

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | PIEP7 | PIEP6 | PIEP5 | PIEP4 | PIEP3 | PIEP2 | PIEP1 | PIEP0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-28 Port P Interrupt Enable Register (PIEP)

Read: Anytime.

Write: Anytime.

This register disables or enables on a per pin basis the edge sensitive external interrupt associated with port P.

PIEP[7:0] — Interrupt Enable Port P

1 =Interrupt is enabled.

0 = Interrupt is disabled (interrupt flag masked).

#### Address Offset: \$\_\_1F

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | PIFP7 | PIFP6 | PIFP5 | PIFP4 | PIFP3 | PIFP2 | PIFP1 | PIFP0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-29 Port P Interrupt Flag Register (PIFP)

Read: Anytime.

Write: Anytime.

Each flag is set by an active edge on the associated input pin. This could be a rising or a falling edge based on the state of the PPSP register. To clear this flag, write "1" to the corresponding bit in the PIFP register. Writing a "0" has no effect.

PIFP[7:0] — Interrupt Flags Port P

1 = Active edge on the associated bit has occurred (an interrupt will occur if the associated enable bit is set).

Writing a "1" clears the associated flag.

0 =No active edge pending.

Writing a "0" has no effect.

### 3.1.5 Port H Registers

#### Address Offset:\$\_\_20 6 Bit 7 5 4 3 2 1 Bit 0 Read: PTH7 PTH6 PTH5 PTH4 PTH3 PTH2 PTH1 PTH0 Write: SPI: SS1 SCK1 MOSI1 MISO1 Reset: 0 0 0 0 0

Figure 3-30 Port H I/O Register (PTH)

Read: Anytime.

Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

The SPI function takes precedence over the general purpose I/O function associated with if enabled. Refer to *HSC12 Serial Peripheral Interface (SPI) Block Guide* (Motorola document order number, S12SPIV2/D) for details.

Figure 3-31 Port H Input Register (PTIH)

Read: Anytime.

Write: Never, writes to this register have no effect.

This register always reads back the status of the associated pins. This can also be used to detect overload or short circuit conditions on output pins.

#### Address Offset: \$\_\_22

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | DDRH7 | DDRH6 | DDRH5 | DDRH4 | DDRH3 | DDRH2 | DDRH1 | DDRH0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-32 Port H Data Direction Register (DDRH)

Read: Anytime.

Write: Anytime.

This register configures each port H pin as either input or output.

DDRH[7:0] — Data Direction Port H

1 = Associated pin is configured as output.

0 =Associated pin is configured as input.

Due to internal synchronization circuits, it can take up to 2 bus cycles until the correct value is read on PTH or PTIH registers, when changing the DDRH register.

#### Address Offset: \$\_\_23

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |  |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Read:<br>Write: | RDRH7 | RDRH6 | RDRH5 | RDRH4 | RDRH3 | RDRH2 | RDRH1 | RDRH0 |  |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |

Figure 3-33 Port H Reduced Drive Register (RDRH)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each port H output pin as either full or reduced. If the port is used as input this bit is ignored.

RDRH[7:0] — Reduced Drive Port H

1 = Associated pin drives at reduced drive strength.

0 = Full drive strength at output.

# Freescale Semiconductor, Inc.— S12A128PIMV1/D, Rev. 1

#### Address Offset: \$ 24

Figure 3-34 Port H Pull Device Enable Register (PERH)

Read: Anytime.

Write: Anytime.

This register configures whether a pull-up or a pull-down device is activated, if the port is used as input. This bit has no effect if the port is used as output. Out of reset no pull device is enabled.

PERH[7:0] — Pull Device Enable Port H

- 1 = Either a pull-up or pull-down device is enabled.

- 0 = Pull-up or pull-down device is disabled.

#### Address Offset: \$\_\_25

Figure 3-35 Port H Polarity Select Register (PPSH)

Read: Anytime.

Write: Anytime.

This register serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.

PPSH[7:0] — Polarity Select Port H

- 1 = Rising edge on the associated port H pin sets the associated flag bit in the PIFH register. A pull-down device is connected to the associated port H pin, if enabled by the associated bit in register PERH and if the port is used as input.

- 0 = Falling edge on the associated port H pin sets the associated flag bit in the PIFH register. A pull-up device is connected to the associated port H pin, if enabled by the associated bit in register PERH and if the port is used as input.

#### Address Offset: \$\_\_26

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | PIEH7 | PIEH6 | PIEH5 | PIEH4 | PIEH3 | PIEH2 | PIEH1 | PIEH0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-36 Port H Interrupt Enable Register (PIEH)

Read: Anytime.

Write: Anytime.

This register disables or enables on a per pin basis the edge sensitive external interrupt associated with port H.

PIEH[7:0] — Interrupt Enable Port H

1 = Interrupt is enabled.

0 = Interrupt is disabled (interrupt flag masked).

#### Address Offset: \$\_\_27

|                 | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:<br>Write: | PIFH7 | PIFH6 | PIFH5 | PIFH4 | PIFH3 | PIFH2 | PIFH1 | PIFH0 |

| Reset:          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Figure 3-37 Port H Interrupt Flag Register (PIFH)

Read: Anytime.

Write: Anytime.

Each flag is set by an active edge on the associated input pin. This could be a rising or a falling edge based on the state of the PPSH register. To clear this flag, write "1" to the corresponding bit in the PIFH register. Writing a "0" has no effect.

PIFH[7:0] — Interrupt Flags Port H

1 = Active edge on the associated bit has occurred (an interrupt will occur if the associated enable bit is set).

Writing a "1" clears the associated flag.

0 =No active edge pending.

Writing a "0" has no effect.

#### 3.1.6 Port J Registers

#### Address Offset: \$ 28 Bit 7 6 5 3 2 Bit 0 0 0 0 0 Read: PTJ7 PTJ6 PTJ1 PTJ0 Write: SCL SDA IIC: 0 0 Reset: = Reserved or unimplemented

Figure 3-38 Port J I/O Register (PTJ)

Read: Anytime.

Write: Anytime.

If the data direction bits of the associated I/O pins are set to 1, a read returns the value of the port register, otherwise the value at the pins is read.

PJ[7:6]

The IIC function (SCL and SDA) takes precedence over the general purpose I/O function if the IIC is enabled. If the IIC module takes precedence, the SDA and SCL outputs are configured as open drain outputs. Refer to *HCS12 Inter-Integrated Circuit (IIC) Block Guide* (Motorola document order number, S12IICV2/D) for details.

Figure 3-39 Port J Input Register (PTIJ)

Read: Anytime.

Write: Never, writes to this register have no effect.

This register always reads back the status of the associated pins. This can be used to detect overload or short circuit conditions on output pins.

#### Address Offset: \$\_\_2A Bit 7 6 5 3 2 1 Bit 0 Read: 0 0 0 0 DDRJ7 DDRJ6 DDRJ1 DDRJ0 Write: 0 Reset: 0 0 = Reserved or unimplemented

Figure 3-40 Port J Data Direction Register (DDRJ)

Read: Anytime.

Write: Anytime.

This register configures each port J pin as either input or output.

The IIC takes control of the I/O if enabled. In this case, the data direction bits will not change. The DDRJ bits revert to controlling the I/O direction of a pin when the IIC module is disabled.

DDRJ[7:6][1:0] — Data Direction Port J

1 = Associated pin is configured as output.

0 =Associated pin is configured as input.

Due to internal synchronization circuits, it can take up to 2 bus cycles until the correct value is read on PTJ or PTIJ registers, when changing the DDRJ register.

Figure 3-41 Port J Reduced Drive Register (RDRJ)

Read: Anytime.

Write: Anytime.

This register configures the drive strength of each port J output pin as either full or reduced. If the port is used as input this bit is ignored.

RDRJ[7:6][1:0] — Reduced Drive Port J

1 = Associated pin drives at reduced drive strength.

0 =Full drive strength at output.

#### Address Offset: \$ 2C Bit 7 6 5 3 2 1 Bit 0 Read: 0 0 0 0 PERJ7 PERJ1 PERJ6 PERJ0 Write: Reset: 1 = Reserved or unimplemented

Figure 3-42 Port J Pull Device Enable Register (PERJ)

Read: Anytime.

Write: Anytime.

This register configures whether a pull-up or a pull-down device is activated, if the port is used as input or as wired-or output. This bit has no effect if the port is used as push-pull output. Out of reset a pull-up device is enabled.

PERJ[7:6][1:0] — Pull Device Enable Port J

1 = Either a pull-up or pull-down device is enabled.

0 = Pull-up or pull-down device is disabled.

#### Address Offset: \$ 2D

Figure 3-43 Port J Polarity Select Register (PPSJ)

Read: Anytime.

Write: Anytime.

This register serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.

PPSJ[7:6][1:0] — Polarity Select Port J

- 1 = Rising edge on the associated port J pin sets the associated flag bit in the PIFJ register. A pull-down device is connected to the associated port J pin, if enabled by the associated bit in register PERJ and if the port is used as input.

- 0 = Falling edge on the associated port J pin sets the associated flag bit in the PIFJ register. A pull-up device is connected to the associated port J pin, if enabled by the associated bit in register PERJ and if the port is used as general purpose input or as IIC port.

#### Address Offset: \$\_\_2E Bit 7 6 5 4 3 2 1 Bit 0 Read: 0 0 0 0 PIEJ7 PIEJ1 PIEJ6 PIEJ0 Write: 0 Reset: 0 0 0 = Reserved or unimplemented

Figure 3-44 Port J Interrupt Enable Register (PIEJ)

Read: Anytime.

Write: Anytime.

This register disables or enables on a per pin basis the edge sensitive external interrupt associated with port I

PIEJ[7:6][1:0] — Interrupt Enable Port J

1 = Interrupt is enabled.

0 = Interrupt is disabled (interrupt flag masked).

Address Offset: \$ 2F

Figure 3-45 Port J Interrupt Flag Register (PIFJ)

Read: Anytime.

Write: Anytime.

Each flag is set by an active edge on the associated input pin. This could be a rising or a falling edge based on the state of the PPSJ register. To clear this flag, write "1" to the corresponding bit in the PIFJ register. Writing a "0" has no effect.

PIFJ[7:6][1:0] — Interrupt Flags Port J

1 = Active edge on the associated bit has occurred (an interrupt will occur if the associated enable bit is set).

Writing a "1" clears the associated flag.

0 =No active edge pending.

Writing a "0" has no effect.

# **Section 4 Functional Description**

#### 4.1 General

Each pin can act as general purpose I/O. In addition the pin can act as an output from a peripheral module or an input to a peripheral module.

A set of configuration registers is common to all ports. All registers can be written at any time, however a specific configuration might not become active.

Example:

Selecting a pull-up resistor. This resistor does not become active while the port is used as a push-pull output.

## 4.1.1 I/O Register

This register holds the value driven out to the pin if the port is used as a general purpose I/O.

Writing to this register has only an effect on the pin if the port is used as general purpose output. When reading this address, the value of the pins is returned if the data direction register bits are set to 0.

If the data direction register bits are set to 1, the contents of the I/O register is returned. This is independent of any other configuration (**Figure 4-1**).

### 4.1.2 Input Register

This is a read-only register and always returns the value of the pin (Figure 4-1).

### 4.1.3 Data Direction Register

This register defines whether the pin is used as an input or an output.

If a peripheral module controls the pin the contents of the data direction register is ignored (**Figure 4-1**).

Figure 4-1 Illustration of I/O Pin Functionality

## 4.1.4 Reduced Drive Register

If the port is used as an output the register allows the configuration of the drive strength.

### 4.1.5 Pull Device Enable Register

This register turns on a pull-up or pull-down device.

It becomes only active if the pin is used as an input or as a wired-or output.

# 4.1.6 Polarity Select Register

This register selects either a pull-up or pull-down device if enabled.

It becomes only active if the pin is used as an input. A pull-up device can be activated if the pin is used as a wired-or output.

### 4.2 Port T

This port is associated with the ECT module.

Port T pins PT[7:0] can be used for either general-purpose I/O, or with the channels of the Enhanced Capture Timer.

During reset, port T pins are configured as high-impedance inputs.

#### 4.3 Port S

This port is associated with SCI0, SCI1 and SPI0.

Port S pins PS[7:0] can be used either for general-purpose I/O, or with the SCI and SPI subsystems.

During reset, port S pins are configured as inputs with pull-up.

The SPI0 pins can be re-routed. Refer to **Figure 3-21**.

#### 4.4 Port M

This port is associated with the SPI0.

Port M pins PM[7:0] can be used for either general purpose I/O, or with the SPI subsystem.

During reset, port M pins are configured as high-impedance inputs.

The SPI0 pins can be re-routed. Refer to **Figure 3-21**.

#### 4.4.1 Module Routing Register

This register allows the user to re-route the SPI0 and SPI1 pins to predefined pins.

**NOTE:** The purpose of the Module Routing Register is to provide maximum flexibility for future derivatives of the MC9S12A256 with a lower number of SPI modules.

Table 4-1 Implemented Modules on Derivatives

| Number of Modules | SPI0 | SPI1 |

|-------------------|------|------|

| 2                 | Х    | Х    |

| 1                 | Х    | ı    |

Refer to **Figure 3-21** for further information.

### 4.5 Port P

This port is associated with the PWM and SPI1.

Port P pins PP[7:0] can be used for either general purpose I/O, or with the PWM and SPI subsystems.

The pins are shared between the PWM channels and the SPI1 module. If the PWM is enabled, the pins become PWM output channels with the exception of pin 7 which can be PWM input or output. If SPI1 is enabled and the PWM is disabled, the respective pin configuration is determined by several status bits in the SPI modules.

During reset, port P pins are configured as high-impedance inputs.

The SPI1 pins can be re-routed. Refer to **Figure 3-21**.

Port P offers 8 I/O pins with edge triggered interrupt capability in wired-or fashion. The interrupt enable as well as the sensitivity to rising or falling edges can be individually configured on per pin basis. All 8 bits/pins share the same interrupt vector. Interrupts can be used with the pins configured as inputs or outputs.

An interrupt is generated when a bit in the port interrupt flag register and its corresponding port interrupt enable bit are both set. This external interrupt feature is capable to wake up the CPU when it is in STOP or WAIT mode.

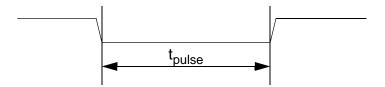

A digital filter on each pin prevents pulses (**Figure 4-3**) shorter than a specified time from generating an interrupt. The minimum time varies over process conditions, temperature and voltage (**Figure 4-2** and **Table 4-2**).

Figure 4-2 Interrupt Glitch Filter on Port P, H, and J (PPS=0)

|           | Mode                       |                   |                                                            |  |  |  |

|-----------|----------------------------|-------------------|------------------------------------------------------------|--|--|--|

| Pulse     | STOR                       | STOP <sup>1</sup> |                                                            |  |  |  |

|           |                            | Unit              |                                                            |  |  |  |

| Ignored   | t <sub>pulse</sub> ≤ 3     | bus clocks        | $t_{pulse} \le t_{pign}$                                   |  |  |  |

| Uncertain | 3 < t <sub>pulse</sub> < 4 | bus clocks        | t <sub>pign</sub> < t <sub>pulse</sub> < t <sub>pval</sub> |  |  |  |

| Valid     | t <sub>pulse</sub> ≥ 4     | bus clocks        | $t_{pulse} \ge t_{pval}$                                   |  |  |  |

**Table 4-2 Pulse Detection Criteria**

#### NOTES:

These values include the spread of the oscillator frequency over temperature, voltage and process.

Figure 4-3 Pulse Illustration

A valid edge on an input is detected if 4 consecutive samples of a passive level are followed by 4 consecutive samples of an active level directly or indirectly.

The filters are continuously clocked by the bus clock in RUN and WAIT mode. In STOP mode the clock is generated by a single RC oscillator in the Port Integration Module. To maximize current saving the RC oscillator runs only if the following condition is true on any pin:

Sample count <= 4 and port interrupt enabled (PIE=1) and port interrupt flag not set (PIF=0).

#### 4.6 Port H

This port is associated with the SPI1.

Port H pins PH[7:0] can be used for either general purpose I/O, or with the SPI subsystem.

During reset, port H pins are configured as high-impedance inputs.

Port H pins can be used with the routed SPI1 module. Refer to **Figure 3-21**.

Port H offers 8 I/O ports with the same interrupt features as port P.

#### 4.7 Port J

This port is associated with the IIC.

Port J pins PJ[7:6] and PJ[1:0] can be used for either general purpose I/O, or with the IIC subsystem.

During reset, port J pins are configured as inputs with pull-up.

If IIC takes precedence the pins become IIC open-drain output pins.

Port J offers 4 I/O ports with the same interrupt features as port P.

## 4.8 Port A, B, E, K, and BKGD pin

All port and pin logic is located in the core module. Refer to MEBI in *HCS12 Core User Guide* (Motorola order number, HCS12COREUG/D) for details.

# 4.9 External Pin Descriptions

All ports start up as general purpose inputs on reset.

# 4.10 Low Power Options

#### 4.10.1 Run Mode

No low power options exist for this module in run mode.

### 4.10.2 Wait Mode

No low power options exist for this module in wait mode.

### 4.10.3 Stop Mode

All clocks are stopped. There are asynchronous paths to generate interrupts from STOP on port P, H and J.

# **Section 5 Resets**

#### 5.1 General

The reset values of all registers are given in **3.1 Register Descriptions**.

## 5.2 Reset Initialization

All registers including the data registers get set/reset asynchronously. **Table 5-1** summarizes the port properties after reset initialization.

**Table 5-1 Port Reset State Summary**

|          | Reset States                                                                                                     |              |            |                  |           |  |  |