| Name: | CM Box: |

|-------|---------|

|       |         |

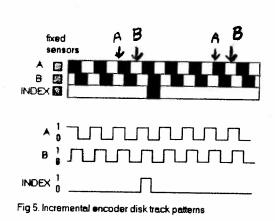

1) Consider the incremental shaft position encoder shown in Fig. 5. Show TWO possible positions of LED/PT pair A (using arrows) and also TWO possible positions of LED/PT pair B that will produce the same A and B waveforms shown in Fig. 6 using ONLY the TOP encoding strip (thereby greatly simplifying the encoder wheel).

(Materials taken from Introduction to Mechatronics and Measurement Systems, Histand & Alciatore, 1999 McGraw Hill)

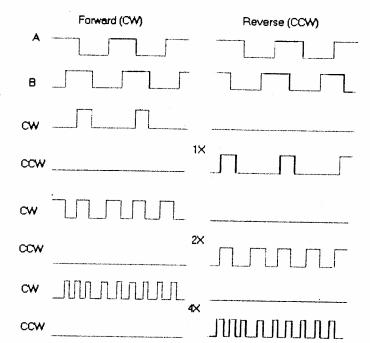

Fig 6. Quadrature direction sensing and resolution enhancement. (CW = clockwise, CCW= counter-clockwise)

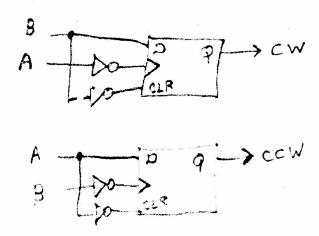

2) Using only rising-edge sensitive D flip-flops (with D, CLK, CLR, Q and Q\ pins) and assorted inverters and logic gates, design a circuit that will derive the 1x resolution CW and CCW output waveforms shown in Fig. 6 from the A and B input waveforms.

3) Now using the same components as in Problem 2, design a sequential circuit that produces the 2x resolution CW and CCW outputs shown in Fig. 5. What is the advantage of the circuit of Problem 3 over the circuit of Problem 2?

- 4) Referring to Slide #39, imagine the two device rectangles are separated by about 1/4 mile. If the ground potentials at the two device rectangles differ (say due to a lightning strike occurring closer to the bottom device)  $\Rightarrow$  V<sub>1</sub> unequal to 0

- a) Why would the 2-conductor cable burn out if the optocoupler circuit were omitted?

b) What problem would occur if the optocoupler were omitted and we chose to use a 1 conductor cable (leaving out the ground conductor)?

Jufference V, may be as high as 2500 V before arcing occurs and driven device burns out.

What is the purpose of the 3.3 kp resistor and the 1N914 diode?

3.3 &A Limits current to LED inside optocouplar (Protects LED and IN914 protects LED in case (-) Voltage applied across optocoupler...

e) Light from the LED falls upon the reverse-biased photodiode junction and causes elevated electron-hole pair generation in its depletion region. This increases the diode's reverse bias current (Idrev) from several nA to several µA. This reverse diode current flows through two Darlington-connected BJT transistors. If both transistors have a beta of 30 and the LED light stimulates a photodiode current of Idrev = 2  $\mu$ A, demonstrate that the output voltage developed at the output of the optocoupler and ground (between the bottom of the 10 k $\Omega$  resistor and ground) is zero.

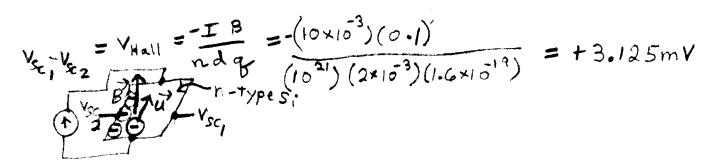

- 5) Refer to Slides 41 and 42.

- a) Calculate the Hall voltage (Vsc1-Vsc2) for the n-type Si Hall Effect probe shown on Slide #41 if B = 0.1 Tesla,  $n = 10^2 1$  m<sup>3</sup>-3, q = 1.6E-19 Coulombs, W = 1 cm, d = 2 mm, I = 10 mA.

b) How would the terminal voltage change if the n-type Si were replaced by p-type Si with the same doping level?

c) How would the terminal voltage of problem (a) change if the applied B field were reversed?

d) Why must the P-type substrate be connected to ground (the lowest potential in the Hall Effect sensor circuit of Slide #43?

Always Keeps N-type conduction sheet isolated From substrate, since paljunction reverse biasets

Assume that the Michigan Serial Sensor/Actuator Bus of Slide #45 implements a one-wire asynchronous bidirectional serial data line the same way the "1-wire" bus was implemented using drivers. As with the "1-wire" bus, this serial data line must be pulled high by an external pullup resistor (not shown). When data bytes are not traveling on this bus, the line idles not be pulled high by an external pullup resistor (not shown). When data bytes are not traveling on this bus, the line idles not be pulled high by the line idles not be sending a byte by pulling low the low of the host computer will begin a read or write transaction by sending a command to a specific node address (see the command format on Slide #46). If the command sent is a read command, the host computer will wait until an addressed node sends one or two data bytes back to the host (depending on whether the flag bit in the command is 0 or 1. If the command sent is a write command, the host sends one or two data bytes to the addressed node. Each byte that is sent starts with a start bit that is always low and ends with a start bit that is always low and ends with a start bit that is always low and ends

- 7) Refer to the Binary Coded digital shaft angle encoder on the LEFT of Slide #47.

- a) Write out all 16 binary codes in the sequence they would be picked up by the brushes (or by the LED/PT pairs) of the binary coded wheel as it rotates CCW.

المار دادام رادام دادام دادام دادام دادام دادام دادام دادام

b) Explain why incorrect position codes may be obtained at any time the wheel rotates to a position that is near to where more than one bits are changing. Consider the worst case, which is shown in this slide, when the wheel is at a position where ALL the bit positions are changing. (Explain why ANY binary code may result at this critical position, in any real-world situation where the brushes will not be perfectly aligned.)

Problem occurs if brushes not aliqued. Consider (1111) + (0000)

Ex: x| |x|

Any binary value

might be read!

XI |x|

NT Misaligned brush

Tolerance

Tolerance

8) Refer to the Gray Coded digital shaft angle encoder on the RIGHT of Slide #47.

a) Write out all 16 Gray codes would be picked up by the brushes (or by the LED/PT pairs) of the Gray coded wheel as it rotates CCW.

b) Explain why there will now be NO incorrect position codes picked up in a practical situation where the brushes are not perfectly aligned.

Now only one bit position changes at a time as we go from one position to another. Only slight position errors can now occur by the amount the brushes are misaligned.

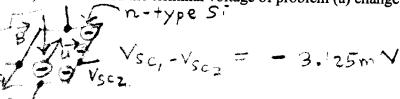

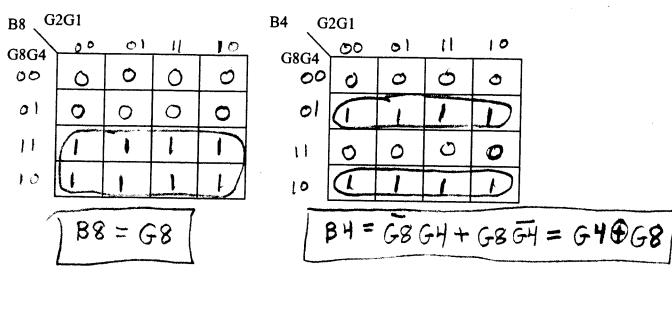

c) One disadvantage of the Gray Coded digital shaft angle encoder is that its output is not binary. To design a combinational logic circuit that will convert the Gray Code result "G8G4G2G1" to binary "B8B4B2B1" make four Karnaugh Maps, one for B8, one for B4, one for B2, and one for B1. Each of these maps must have inputs G8, G4, G2, and G1. Find the simplest possible SOP (sum of products) logic design equations using these K-maps.

| B2                | G2G1    |        |        | B1 G       | 32G1                 |        |      |              |        |

|-------------------|---------|--------|--------|------------|----------------------|--------|------|--------------|--------|

| G                 | 8G4 50  | 01 1   | 1 10   | G8G4       | 90                   | اد     | 11   | 10           |        |

| _                 | 00 0    | 0      |        | ) 0004     | 0                    | 1      | 0    |              |        |

|                   | 01      |        | 0      | 01         | 1                    | 0      | 1    | 0            |        |

|                   | 11 0    | 0 (    |        | 11         | 0                    | 1      | 0    | ŀ            |        |

|                   | 10      | I) $c$ | 0      | 10         | 1                    | 0      | 1    | O            |        |

| 82 = G8 GH G      | 2 + G8  | G46:   |        |            | 68                   | -17    |      | B,           |        |

| + 68646           | 2 + G8  | G4 G=  | 2      |            | 68<br>64<br>62<br>64 | 到      |      | •            | if odd |

| = 52 · (G4G8      | + 64 G8 | ) + G2 | (G4.68 | 8+64·6     | 8/                   |        | Ť    | # of<br>inpu | 15 at  |

|                   | ÐG8)    |        | (G4E   |            |                      |        |      | ,            |        |

| - 2 O             | Conoc   |        |        |            | ,<br>=[68            | (F) G' | 1Ð G | 2£           | G1)    |

| $) = G2 \oplus ($ | (64 G)  | ४)     |        | <i>D</i> ) | -//c                 | @/#\c  | 山田   | G2)(         | () GI) |

| B2 = G2 (+)       | ВЧ      |        | -      | -          | -(((6                |        |      |              |        |

|                   |         |        | 1      | B.         | - (1                 | E B B  | -    |              |        |

|                   |         |        |        | 1          | - 51                 | T/D    |      |              |        |

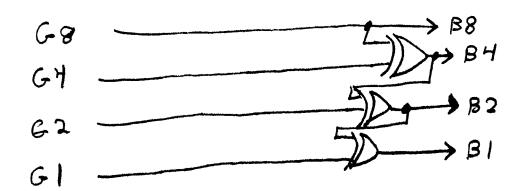

d) Construct a final Gray Code to Binary Code conversion circuit from the results of your K-maps. (Hint: you should be able to construct a 4-bit Gray to Binary decoder with 3 two-input XOR gates!)

- e) How many digits of Gray code are provided by the optical shaft angle encoder wheel shown on Slide 48? \_\_\_\_\_\_

- 9) In the "Poor Man's A/D" circuit of Slide #53, microcontroller output pin RA0 is driven low (0 V) for a long enough time to ensure that C = 0.1 μF has been completely discharged. Then RA0 is suddenly changed to an input pin by changing its DDR register bit. Let us assume that RA0 changes from 0 to 1 as its voltage level rises above 3.0 V, instead of the value given on the slide. The microcontroller then times how long it takes the RA0 input pin to change from 0 to 1. If this time is found to be 10 ms, find the value of the resistive transducer R. Find the new value of R if this time is doubled (20 ms).