# CSSE232 Computer Architecture I

**Control Hazards**

# Pipelining

• From last time...

- Data Hazards:

- Create units to help with

- Forward data

- Detect when stalls are needed

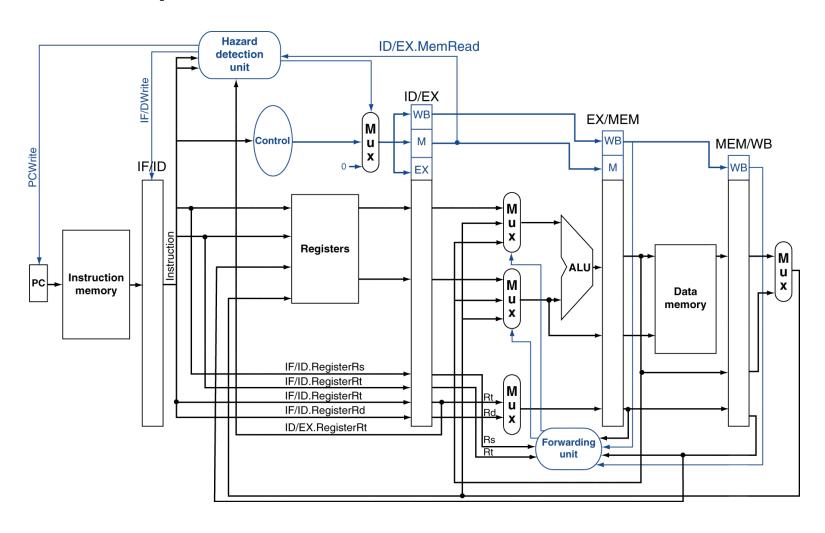

#### Datapath with Hazard Detection

## Branching

- Previous datapaths had no issues with branching

- Pipeline datapath

- Executing several instructions in parallel

- Processing branch and subsequent instructions!

#### **Branch Hazards**

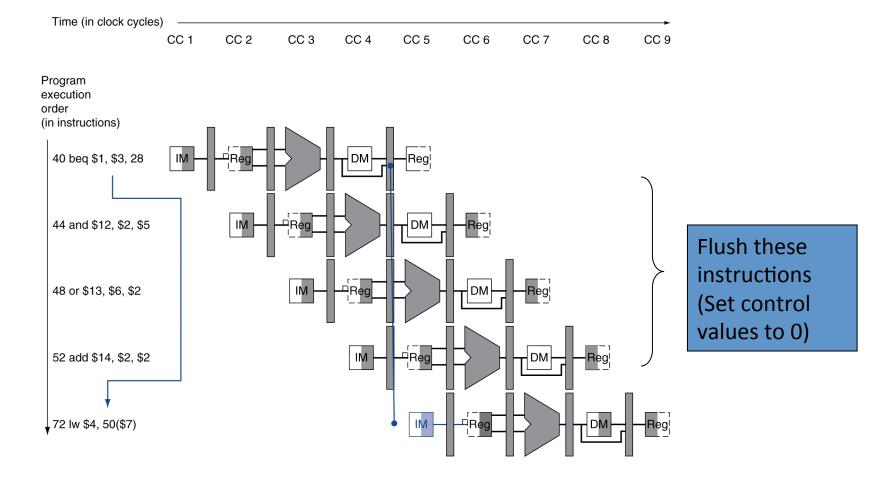

# Flushing

- Stall

- Stopped updates to IF, ID

- Cancelled EX for current instruction

- Flush

- Cancel all instructions!

- Set control to zero in for 3 instructions in flight

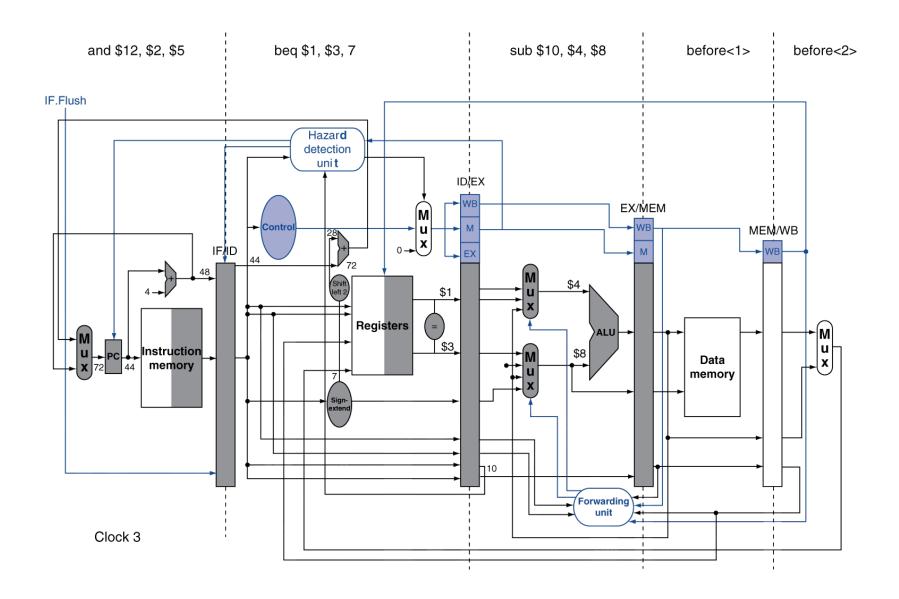

# Reducing Flushed Instructions

How to reduce wasted instructions?

# Reducing Branch Flushing

- Move hardware to determine outcome to ID stage

- Target address adder

- Register comparator

- ALUs are slow

- Subtaction is slow

- Equal is much easier

- Just use XOR gates

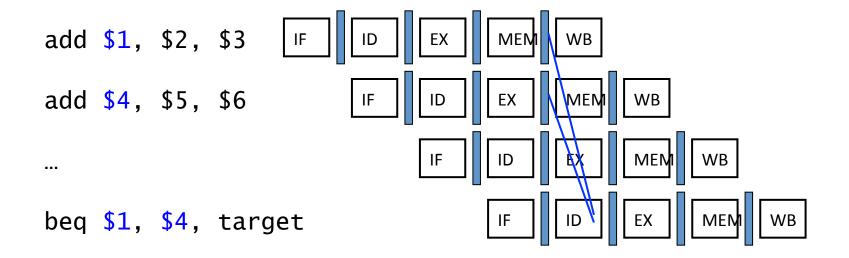

## **Detecting Control Hazard**

- Hazard unit can detect branch instructions, and automatically flush next instruction

- MIPS does not detect control hazards

- Does not flush!

- Will execute 1 instruction after branch

- Require noop after all branches?

- Lets programmer choose to use the 'delay slot'

- Can increment loop counter (or something else)

#### Other Control Hazards

- Jump and link

- Greencard says PC+8

- Assumes a delay slot

- Return to instruction after delay slot

# Other complications

- Flushing is one problem

- MIPS solution is to reduce to single delay slot

What about getting branch ready?

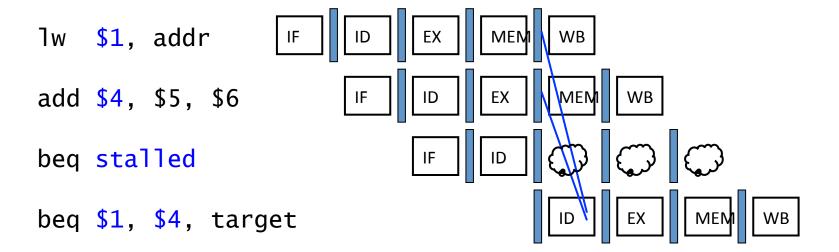

If a comparison register is a destination of 2<sup>nd</sup> or 3<sup>rd</sup> preceding ALU instruction

Can resolve using forwarding

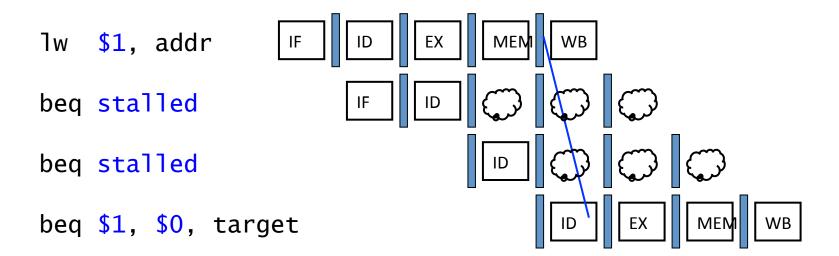

- If a comparison register is a destination of preceding ALU instruction or 2<sup>nd</sup> preceding load instruction

- Need 1 stall cycle

- If a comparison register is a destination of immediately preceding load instruction

- Need 2 stall cycles

#### Dynamic Branch Prediction

- In deeper and superscalar pipelines, branch penalty is more significant

- Use dynamic prediction

- Branch prediction buffer (aka branch history table)

- Indexed by recent branch instruction addresses

- Stores outcome (taken/not taken)

- To execute a branch

- Check table, expect the same outcome

- Start fetching from fall-through or target

- If wrong, flush pipeline and flip prediction

#### **Review and Questions**

- Hazards

- Data

- Control

- Structural

- Hazard detection

- Hazard prevention